Juha-Pekka Soininen

Architecture design methods for application domain-specific integrated computer systems

# Architecture design methods for application domain-specific integrated computer systems

Juha-Pekka Soininen

VTT Electronics

Academic dissertation to be presented with the assent of the Faculty of Technology, University of Oulu, for public discussion in Kajaaninsali (L6), Linnanmaa, Oulu, on May 7th, 2004, at 12 noon.

ISBN 951-38-6363-8 (soft back ed.) ISSN 1235-0621 (soft back ed.)

ISBN 951-38-6364-6 (URL: http://www.vtt.fi/inf/pdf/) ISSN 1455-0849 (URL: http://www.vtt.fi/inf/pdf/)

Copyright © VTT Technical Research Centre of Finland 2004

#### JULKAISIJA - UTGIVARE - PUBLISHER

VTT, Vuorimiehentie 5, PL 2000, 02044 VTT puh. vaihde (09) 4561, faksi (09) 456 4374

VTT, Bergsmansvägen 5, PB 2000, 02044 VTT tel. växel (09) 4561, fax (09) 456 4374

VTT Technical Research Centre of Finland, Vuorimiehentie 5, P.O.Box 2000, FIN-02044 VTT, Finland phone internat. + 358 9 4561, fax + 358 9 456 4374

VTT Elektroniikka, Kaitoväylä 1, PL 1100, 90571 OULU puh. vaihde (08) 551 2111, faksi (08) 551 2320

VTT Elektronik, Kaitoväylä 1, PB 1100, 90571 ULEÅBORG tel. växel (08) 551 2111, fax (08) 551 2320

VTT Electronics, Kaitoväylä 1, P.O.Box 1100, FIN–90571 OULU, Finland phone internat. + 358 8 551 2111, fax + 358 8 551 2320

Technical editing Leena Ukskoski

Soininen, Juha-Pekka. Architecture design methods for application domain-specific integrated computer systems. Espoo 2004. VTT Publications 523. 118 p. + app. 51 p.

**Keywords** decision support methods, quality estimations, mappability estimation, platform based design

## **Abstract**

The role of the single computer inside application-specific integrated circuits is changing with the increasing capacity of semiconductor technology. The system functionality can be partitioned to a set of communicating application domain-specific computers instead of developing the most efficient general-purpose computers that fulfil all kinds of computing needs. The main design challenges are the complexity and diversity of application-domains and the complexity of platforms which can provide enough capacity for those applications.

The architecture design methods presented in this thesis are targeted at application domain-specific computers that are implemented as integrated circuits. Backbone-platform-system design methodology separates the technology, platform design efficiency and application development problems from each other. It also provides a system design framework for the architecture design methods presented. The methods are based on complexity, mappability, and capacity-based quality estimations that are used as decision support and quality validation tools. Abstract models of both applications and architectures enable rapid estimations and adequate coverage in design space exploration.

The methods have been applied to various case examples. Complexity-based estimation provided a systematic approach to the selection of an architecture template that takes into account the changes in technologies and design efficiency. Mappability-based processor-algorithm quality estimation enabled us to study more than 10,000 processor architectures for WLAN modem transceiver example. Capacity-based quality estimation was used in the performance evaluation of configurable multiprocessor architecture. In all cases the respective simulations using for example instruction-set simulators would have taken much longer and required advanced post-processing of results.

## **Preface**

This research was carried out in VTT Electronics between 1999 and 2002. Most of the research was done in MULTICS, SCIFI and NOCARC projects. I want to express my gratitude to all companies involved in those projects and, especially, to Tekes for funding them.

Very many people have supported, encouraged and inspired me during this work. Docent Martti Forsell and Research Professor Aarne Mämmelä have constantly encouraged me, guided me into scientific research methods and emphasized the importance of research and education. Mr. Kari Tiensyrjä has been in a key role in setting up the research projects and research atmosphere in which this work has been done. This thesis would not have been possible without his help. Mr. Jari Kreku, Mr. Antti Pelkonen, and Mr. Jussi Roivainen have been developing and implementing the ideas in this thesis with me. Their role has been indispensable and I owe them a lot.

Mr. Tapio Rautio, Ms. Anu Purhonen, Mr. Klaus Melakari and Mr. Mika Kasslin from Nokia provided a lot of interesting ideas during the MULTICS project. The large steering group of the SCIFI project was a challenging and productive discussion forum. The comments and feedback from all the steering group members and the project group was extremely valuable. In the NOCARC project the co-operation with Royal Institute of Technology in Sweden, and Nokia and Ericsson resulted in an excellent exchange of ideas. The discussions and co-operation with Professor Axel Jantsch and Professor Shashi Kumar from the Royal Institute of Technology and Mr. Klaus Kronlöf from Nokia was very fruitful.

I also appreciate the work of all the other co-authors of original papers not mentioned so far, i.e. Ms. Sandrine Boumard, Professor Ahmed Hemani, Professor Hannu Heusala, Mr. Michael Millberg, Professor Petri Mähönen, Mr. Yang Qu, Mr. Jussi Riihijärvi, Mr Mika Saaranen, Mr Tommi Salminen, and Professor Johnny Öberg.

VTT has supported me in this work by providing excellent research facilities and working environment. I want to thank the management and all the people at VTT. I especially want to thank the support services at VTT Electronics.

Because of their professional way of managing everything from travelling arrangements to daily routines, I have been able to concentrate on my research work

I want to thank Professor Hannu Heusala for supervising this thesis and for several encouraging discussions. I also wish to thank Professor Jari Nurmi and Professor Rolf Ernst, the reviewers of the thesis, for their comments and suggestions.

I want to thank HPY:n tutkimussäätiö and Seppo Säynäjäkankaan tiedesäätiö for their very motivating and important economical support.

Matti and Vappu Turunen let me to use their apartment as a peaceful place to complete this thesis. Most of this thesis was written there during November 2002 and October 2003. Thank you. Kiitos.

Finally, I want to thank my wife Tuija and our children Ulla and Otto for their patience and support. Allowing one to concentrate on the work is one part of it; the other part is to force the mind to think about the more important issues, such as simulated combat flights.

Juha-Pekka Soininen

7 2 2004

# List of original papers

This thesis includes seven original papers published in scientific international journals or proceedings of international conferences. They are included here with the permissions of the original publishers.

- Kumar, S., Jantsch, A., Soininen, J.-P., Forsell, M., Millberg, M., Öberg, J., Tiensyrjä, K. and Hemani, A. A Network on Chip Architecture and Design Methodology. *Proceedings of 2002 IEEE Computer Society Annual Symposium on VLSI*, Pittsburgh, Pennsylvania, USA, 24–25 April 2002. IEEE Computer Society Press 2002. Pp. 117–124.

- Soininen, J.-P., Forsell, M., Pelkonen, A., Kreku, J., Jantsch, A. and Kumar, S. Extending platform based design to Network on Chip systems. *Proceedings of 16<sup>th</sup> International Conference on VLSI Design 2003*, New Delhi, India, 4–8 January 2003. IEEE Computer Society Press 2003. Pp. 401–408.

- 3. Roivainen, J., Riihijärvi, J., Mähönen, P., Soininen, J.-P. and Saaranen, M. Minimisation of functionality and implementation of embedded low-power WWW-server. *Electronics Letters* 2002. Vol. 38, No. 2, pp. 100–101.

- 4. Soininen, J.-P., Boumard, S., Salminen, T. and Heusala, H. Application of decision-making method for architecture selection of ADSL modem. *Proceedings of Euromicro Symposium on Digital Systems Design, DSD 2001*, Warsaw, Poland, 4–6 September 2001. IEEE Computer Society Press 2001. Pp. 21–28.

- Soininen, J.-P., Kreku, J., Qu, Y. and Forsell, M. Mappability Estimation Approach for Processor Architecture Evaluation. *Proceeding of 20<sup>th</sup> NORCHIP Conference 2002*, Copenhagen, Denmark, 11–12 November 2002. Technoconsult, Cogenhagen NV, Denmark 2002. Pp. 171–176.

- Soininen, J.-P., Kreku, J., Qu, Y. and Forsell, M. Fast Processor Core Selection for WLAN Modem using Mappability Estimation. *Proceedings of the 10<sup>th</sup> International Symposium on Hardware/Software Codesign*, CODES 2002, Estes Park, Colorado, USA, 6–8 May 2002. ACM Press 2002. Pp. 61–66.

7. Soininen, J.-P., Pelkonen, A. and Roivainen, J. Configurable Memory Organisation for Communication Applications. *Proceedings of Euromicro Symposium on Digital System Design, DSD2002*, Dortmund, Germany, 4–6 September 2002. IEEE Computer Society Press 2002. Pp. 86–93.

I was the principal author of all except Paper 1 and Paper 3. However, my contributions to these papers have also been essential.

# **Contents**

| Ab  | stract                                                     | İ                                              |                                                | 3  |

|-----|------------------------------------------------------------|------------------------------------------------|------------------------------------------------|----|

| Pre | face                                                       |                                                |                                                | 4  |

| Lis | t of c                                                     | riginal                                        | papers                                         | 6  |

| Lis | t of a                                                     | cronym                                         | ns                                             | 10 |

| 1.  | Intro                                                      | duction                                        | 1                                              | 15 |

|     | 1.1                                                        | Problem definition                             |                                                |    |

|     | 1.2                                                        | Research hypothesis                            |                                                |    |

|     | 1.3                                                        | Research methods                               |                                                |    |

|     | 1.4                                                        | Organ                                          | nisation of thesis                             | 22 |

| 2.  | Design methods for IC-based systems                        |                                                |                                                | 24 |

|     | 2.1                                                        | Basic blocks of integrated computers           |                                                |    |

|     | 2.2                                                        | Models and languages                           |                                                |    |

|     | 2.3                                                        | Desig                                          | n flows                                        | 33 |

|     |                                                            | 2.3.1                                          | Dedicated hardware systems                     | 35 |

|     |                                                            | 2.3.2                                          | Computer-based system design                   | 39 |

|     |                                                            | 2.3.3                                          | System-on-Chip design                          |    |

|     | 2.4                                                        | System-level design methodologies              |                                                |    |

|     | 2.5                                                        | Quality validation                             |                                                | 50 |

|     |                                                            | 2.5.1                                          | Performance evaluation.                        | 52 |

|     |                                                            | 2.5.2                                          | Estimation methods                             | 54 |

| 3.  | Architecture design challenges in future SoC-based systems |                                                |                                                | 59 |

|     | 3.1                                                        | Technology capacity                            |                                                |    |

|     | 3.2                                                        | Product requirements and economics             |                                                |    |

|     | 3.3                                                        | Management of diversity and complexity         |                                                |    |

| 4.  | Architecture design                                        |                                                |                                                |    |

|     | 4.1                                                        | .1 Backbone–Platform–System design methodology |                                                |    |

|     |                                                            | 4.1.1                                          | Separation of layers                           |    |

|     |                                                            | 4.1.2                                          | Separation of infrastructure from applications | 69 |

|     |                                                            | 4.1.3                                          | Design flow                                    | 70 |

|    | 4.2   | Design                      | n of application domain-specific computer              | 72 |

|----|-------|-----------------------------|--------------------------------------------------------|----|

|    |       | 4.2.1                       | Definition of concept model of architecture            | 76 |

|    |       | 4.2.2                       | Definition of implementations of architectural objects | 77 |

|    | 4.3   | .3 Decision support methods |                                                        | 79 |

|    |       | 4.3.1                       | Complexity-based quality estimation                    | 80 |

|    |       | 4.3.2                       | Mappability-based quality estimation                   | 83 |

|    |       | 4.3.3                       | Capacity-based quality estimation                      | 87 |

| 5. | Intro | duction                     | to papers                                              | 91 |

| 6. | Con   | clusions                    | S                                                      | 94 |

| Re | feren | ces                         |                                                        | 97 |

| Αŗ | pend  | ices                        |                                                        |    |

|    | Pape  | rs I–VII                    |                                                        |    |

Appendices of this publication are not included in the PDF version.

Please order the printed version to get the complete publication

(http://www.vtt.fi/inf/pdf/)

# List of acronyms

ACM Association for Computing Machinery

ADSL Asymmetric Digital Subscriber Line

ALAP As Late As Possible

ALU Arithmetic Logic Unit

ASAP As Soon As Possible

ASIC Application Specific Integrated Circuit

ASIP Application Specific Instruction-set processor

ATPG Automated Test Pattern Generation

BiCMOS Bipolar Complementary Metal-Oxide Semiconductor

BPS Backbone-Platform-System design methodology

CAD Computer Aided Design

CFI CAD Framework Initiative

CFSM Communicating Finite State Machine

CIF Caltech Intermediate Format

CISC Complex Instruction Set Computer

CMOS Complementary Metal-Oxide Semiconductor

COTS Commercial Off-The-Shelf

CPI Cycles Per Instruction

CPU Central Processing Unit

DASC Design Automation Standards Committee

DLP Data Level Parallelism

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

DSP Digital Signal Processing

EDA Electronic Design Automation

EDIF Electronic Design Interchange Format

FFT Fast Fourier Transform

FOM Figure Of Merit

FPGA Field Programmable Gate Array

FSM Finite State Machine

GDSII Graphic Design System II

GPP General-Purpose Processor

HDL Hardware Description Language

HW Hardware

I/O Input/Output

IBM International Business Machines

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IHIP Information Highway Interface Platform

ILP Instruction Level Parallelism

IP Intellectual Property or Internet Protocol

IPC Instructions Per Cycle

ISA Instruction Set Architecture

ISS Instruction Set Simulator

ITRS International Technology Roadmap for Semiconductors

MAC Multiply and Accumulate

MESCAL Modern Embedded Systems, Compilers, Architectures, and

Languages project

MIPS Million Instructions Per Second

MMX Multimedia extension

MOPS Million Operations Per Second

MPEG Moving Picture Expert Group

NoC Network on Chip

PC Personal Computer

PDA Personal Digital Assistant

PLD Programmable Logic Device

PLP Program Level Parallelism

QFD Quality Function Deployment

RASSP Rapid prototyping of Application-Specific Signal Processors

RDPA Reconfigurable Data Path Array

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RTL Register Transfer Level

RTOS Real Time Operating System

SMS Short Message Service

SoC System on Chip

SOI Silicon On Insulator

SRAM Static Random Access Memory

SW Software

TLP Thread Level Parallelism

TOSCA Tools for System Co-design Automation

TSMC Taiwan Semiconductor Manufacturing Company

UML Unified Modeling Language

WAP Wireless Access Protocol

VCI Virtual Component Interface

VCX Virtual Component eXhange

VHDL Very High Speed Integrated Circuit Hardware Description

Language

VIS Visual Instruction Set

WLAN Wireless Local Area Network

VLIW Very Long Instruction Word

VLSI Very Large Scale Integration

VSIA Virtual Socket Interface Alliance

# 1. Introduction

The development of semiconductor technology has been rapid since the invention of an integrated circuit in 1958 by Kilby and Noyce. Since then, the complexity of a single chip, the number of gates, has approximately doubled every 18 months, according to the prediction/estimation known as Moore's law (Moore 1965). Current state-of-the-art processors, such as Pentium4, have more than 40 million transistors in a single chip (Bentley 2001) and the design of over 50 million gates ASICs has already been started (Koehl et al. 2003). The silicon complexity, the number of gates per chip, is the product of chip size and gate density. It measures only the structural complexity of the chip. The silicon capacity, the product of silicon complexity and clock frequency, also measures the functional complexity of the chip. The internal clock frequencies of state-of-the-art chips have increased with the shrinking feature size, and local clocks approaching gigahertz range frequencies are nowadays possible inside ASICs (Carrig 2000).

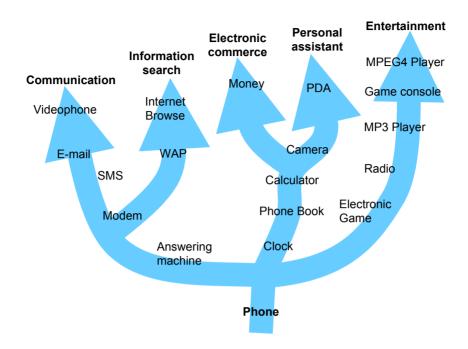

The impact of integrated circuit-based systems on our everyday lives has been enormous. In addition to personal computers (PC) and laptops, we daily use tens of computers that are embedded in products and integrated into application-specific integrated circuits (ASIC). There are integrated circuits and embedded computers, or even computer networks, in clocks, stereos, TVs, ovens, refrigerators, mobile phones, cars, etc. Almost every product that uses electricity nowadays also uses integrated circuit technology. In the year 2000 alone, more than 1 billion embedded processors were being sold and the total value of the semiconductor market was about 200 billion Euro (IC Insights 2001).

The silicon content, the value of integrated circuits, of an electronic product has also increased steadily. The "intelligence" of ASICs has increased. System-on-chip, SoC, is an ASIC that contains one or several processor cores and embedded software. The number of SoC designs has been predicted to outperform the number of standard logic designs in 2003 (IC Insights 2001). According to the international technology roadmap for semiconductors (ITRS 2001), the trend of increasing silicon capacity and structural complexity will continue at least until 2016, when the ultimate physical limits of silicon and manufacturing equipment are reached. This means that from the current 0.13  $\mu$ m technology generation we will move to 90 nm technology in 2004 and 65 nm

technology in 2007. In fact, some news announcements from silicon vendors such as TSMC and IBM indicate development that is even more rapid. The overall maximum complexity of a single chip system in production will increase from 899 million transistors to 1,020 billion transistors and 2,041 billion transistors respectively. In 2016 the complexity will be about 16.3 billion transistors with 22 nm technology.

Computers have been divided into servers, desktop computers and embedded computers (Hennessy & Patterson 2003). Particularly in the high-end embedded computing domain, such as telecommunications and image processing, the optimal processor architectures have been application-specific (Parhi 1999). The applications of embedded computers are typically fixed at system design time and the system designer can optimise his architecture for those specific applications. In general-purpose computing the computer system designer provides computational and storage capacity for general problems. The application domain-specific computers combine the benefits of both approaches for a limited set of application types. The objective is to design platforms for a variety of products or product variants that are optimised for the characteristic requirements of the application types.

The full exploitation of future silicon capacity requires new architecture approaches and new design paradigms. Multiple computers in a single chip (Cesário et al. 2002), message-based communication networks (Guerrier & Greiner 2000), reconfigurable processing arrays (Compton & Hauck 2002), and different embedded memory technologies such as SRAM, DRAM and FLASH are already reality. Traditional computer architectures are not scalable because they will have significant communication and performance overheads. The limitations of ASIC technology, such as power consumption, communication, I/O, testability, etc., will require new solutions. In addition, the required design effort is becoming a major limitation to system complexity.

#### 1.1 Problem definition

The problem with architecture design methodology will be the complexity of the target system. The number of objects in a computer system architecture is increasing rapidly due to the achievements in ASIC technology. The amount of

software and the complexity of software systems are also increasing. The evaluation of design alternatives and the optimisation of system parameters cannot be done using traditional methods because of the required work and resources.

A system-on-chip architect has to integrate the views of other experts in the design team when real systems are developed. Integrated circuit technology sets the boundary that limits the architectural choices. The theory of computing systems and their architectures define alternatives from which the system architect has to choose the basic approach. The application requirements that result from customer needs and expectations give the system architect measures of the goodness of his choices. Finally, the design methodologies, design flows, languages, methods, and tools are the means for organising and executing the system architect's tasks. Architecture design methodology must take these different aspects into account and provide the means for selecting most feasible alternatives.

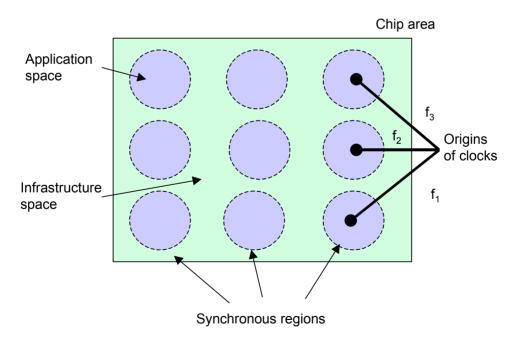

The most significant CMOS technology-dependent architecture design constraints are caused by the signal delays (Sylverster & Keutzer 1999, Ho et al. 2001) and power dissipation. The speed of signal is a constant that depends on the characteristics of the wire. The synchronous design style used in current designs cannot be used when the size of the chip increases, the gate delay decreases and the clock frequency increases. The power dissipation is a problem because every logic operation and signal transition consumes energy and although voltage scaling, etc., can reduce the energy consumption, the overall complexity of the chip increases far more rapidly. It will not be possible to deal with the required electric currents and dissipate the resulting heat.

System-on-Chip architectures are a special case of computer architectures. They have usually been based on RISC processors, DSP processors, embedded SRAM memories and dedicated hardware accelerators. However, the more complex processors and architectures are now becoming feasible as integrated computer architectures as well. Parallel and distributed architectures implementing asynchronous communication schemes and package-based messaging with on-chip networks have also been proposed recently (Guerrier & Greiner 2000, Dally & Towles 2001, Benini & De Micheli 2002). Reconfigurability as an intellectual

property block and new coarse-grain reconfigurable platform has introduced a new dimension to architecture design space (Hartenstein et al. 1996).

In embedded systems, application-specific architectures can lead to better performance and more power efficient solutions. Customisation can be done at various levels from products and architectures to components. The problem is to find the balance between generality and optimality. The identification of a product platform and a product kernel is essential at the product level. At the architectural level the question is how to fix the interconnections between the computational resources and the communication resources. The design space varies from generic interconnect networks to fixed hardware architectures. Reconfigurable processors are examples of design-time customisation at the component level. Optimisation of the instruction-set architecture of the processors for specific applications has been reported to give significant benefits over general-purpose processors (Wang et al. 2001).

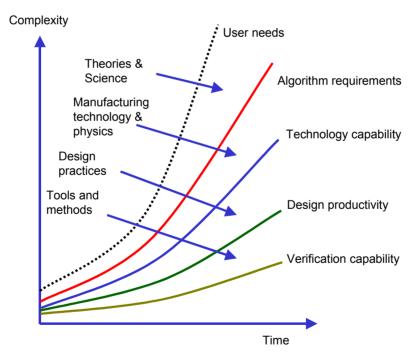

Design productivity is becoming the major obstacle to system-on-chip development. It has increased significantly more slowly than silicon capacity and is, therefore, going to be the limiting factor to the size and complexity of an ASIC. High-level synthesis and higher abstraction levels in design were the first attempts to deal with complexity in the early 1990s. The applicability of the developed approaches turned out to be limited to a very special type of system. Intellectual property block-based design was the second attempt to tackle the problem, but even the extensive reuse of third-party design seems not to be enough. Currently the focus is on platform-based design approaches, where the application and computing platform development are separated from each other, and where the idea is to use existing platforms as a basis onto which new functionalities or resources are added.

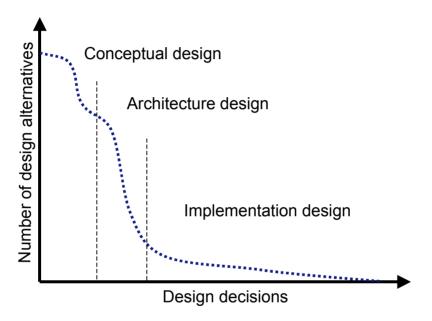

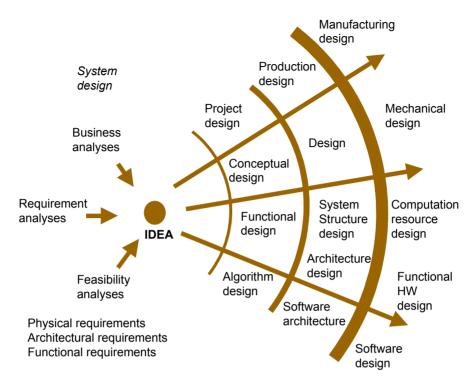

The design process can be viewed as a sequence of design decisions. In the beginning the number of alternative implementations is largest and each decision actually reduces the design space, as depicted in Figure 1. At the end of the process there is only one alternative and the implementation of the product instance remains. Simultaneously, the number of design objects increases and the cost of making changes to the design increases. Therefore, the ability to understand the consequences of early technology and architecture-related decisions are essential in reducing the design costs and time.

The architecture design methodology and design flow depends on the type of system. With fixed hardware architectures, the functional modelling of the final application precedes the structural design. With computer and software-based systems, the processor is designed based on the generic idea of the application software characteristics. The system-on-chip technology enables co-optimisation of both the architecture and the functionality software. Because of complexity, abstract presentations of models and applications are needed, and special focus must be put on decision-making criteria.

Figure 1. The effect of design decisions on the number of possible implementations of the system.

Three approaches are used for system architecture quality estimation today: analytical modelling, simulation and benchmarking (Heidelberger & Lavenberg 1984, Jain 1991). Analytical modelling can be applied when the problems are relatively simple. Benchmarking requires that the hardware is available, and the results are strongly dependent on benchmark program characteristics. In the case of embedded systems in particular, the final application may have so many unique characteristics that benchmarks are not applicable. Simulation alternatives can be used, but in the case of performance simulation the construction of a simulation model requires much work, and in the case of hardware simulation, the simulation performance is a major bottleneck.

# 1.2 Research hypothesis

The objective of the research was to develop methods and techniques that help in making system architecture decisions during system-on-chip design. The particular aim has been to provide fast techniques that use abstract models, and to develop simple estimation algorithms. Component selection, allocation of functionality and performance design are the design activities that differ from traditional electronic system design when complex system platforms are the target. The basic questions that describe the problem are: Why does some computer system architecture give better performance and cost characteristics to some applications than some other architectures? How could we use abstract models for the analysis of the potential of the architecture? The system architecture contains both hardware architecture and software architecture. The methods presented in this thesis are targeted at the hardware architecture design.

The hypothesis in this research is that by applying quality estimation techniques at the architectural level it is possible to distinguish better alternatives from worse, and thereby limit the design space effectively. The applicable estimation techniques include complexity, mappability and capacity estimations.

The complexity-based quality estimation can be used in identifying the capacity boundaries and characteristics of processing and communication resources. The hypothesis in this thesis is that the evaluation of architecture and technology candidates can be done using a complexity estimate-based figure of merits.

The hypothesis in mappability-based quality estimation is that it can reveal the potential of the system before it is actually implemented. This can be done by studying the characteristics of the system from different viewpoints, e.g. by analysing the logical execution flows of algorithms and by studying the operation of the processing resources. Such techniques that can estimate the final quality of a system can be used for helping to decide which components to use, how to modify the components, and what kind of components to use.

With capacity-based quality estimation the hypothesis is that modelling workload characteristics and mapping to architecture capacity models allows rapid and simple evaluations of the quality of architecture. New transaction-level

modelling and simulation methods should be very suitable for these kinds of feasibility studies.

The novelty of the proposed approach is in the chosen abstraction levels, and in the idea of estimating the potential rather than the characteristics of the system model. The benefit of the chosen approach is that the estimators can be simpler because they do not need detailed system models. Secondly, the ability to design an optimal system is not restricted because of abstract models. In this approach optimistic guesses on system quality are made during the estimation. This allows the evaluation of more alternatives more rapidly, which will be a necessity in the future.

#### 1.3 Research methods

Industrial design methodologies for complex systems-on-chips are the results of evolutionary processes inside the companies. Success has depended on the ability to integrate the required competence areas with the ability to learn from mistakes. The role of academic research and the various EDA tool vendors has been to provide the material in the form of theories, methods and tools. Revolutionary, complete solutions for all aspects of SoC design have not been successful so far.

The research method in this thesis follows the evolutionary nature of industrial SoC design methods. The architecture design methodology presented here is a synthesis of technology trends, architecture trends, product market trends, research trends and my background and experience in this field.

The complexity of target architectures is such that the formal, detailed and complete modelling and measurement type of validation is not economically feasible. Therefore, in this thesis the complete design methodology is not validated as such. Instead, the feasibility of the approach is demonstrated by developing three methods, applying them to the case example systems, and comparing the results with more detailed implementations or simulations. Each of the estimation methods studied in this thesis is a potential topic for further research. In this work the focus is on the overall methodology and the estimation methods are only studied to the point where the potential and feasibility is

proven. The value of the overall methodology can only be assessed using common sense and intuition.

### 1.4 Organisation of thesis

This thesis consists of an introduction and seven original papers. The selected papers represent the latest results of the research I have carried out. They have been written between 2000 and 2002. However, the ideas in the thesis are the outcome of fifteen years of research starting from the late 1980s, when ASIC design was taking its first steps in using hardware description languages (HDL) instead of graphical block diagrams.

The introduction of VHDL in 1987 revolutionised ASIC design and enabled the transition from a very structural gate array ASIC to register-transfer level (RTL) synthesis and cell-based designs. At the same time, the technology allowed the integration of a processor core and dedicated logic into the same chip. System modelling, simulation and SW/HW partitioning were research topics that initiated a number of papers. (Juntunen et al. 1988, Soininen et al. 1989, Sipola et al. 1991, Kauppi & Soininen 1991, Kauppi et al. 1992, Sipola et al. 1992)

In the 1990s it was obvious to the research community that using processors in the ASIC enabled new system optimisation possibilities. Silicon technology enabled the integration of more complex processors, embedded memories and analogue functions into the same chip. System-level simulation and verification became more important (Soininen et al. 1995, Soininen et al. 1997, Soininen et al. 1998a). In the late 1990s the system-on-chip projects started to be too expensive and complicated. In order to increase the usability of the design at system-level, the product platform and platform chip concepts were introduced and studied also in Soininen (1997), Soininen et al. (1998b), and Soininen (1999). The first ideas for a new architecture design method were presented in Soininen et al. (2001). The concepts of intellectual property block or virtual component were needed to enable reuse at block level. These issues were studied in Riihijärvi et al. (2001) and Pelkonen et al. (2001).

Today we are facing a paradigm shift from analogue to the introduction of VHDL. SystemC is a new language, which is claimed to integrate software

development and hardware development in a way that enables system-level design. The system designer is again drawing blocks and mapping functionality into them. In architecture research the new computing element array ASICs integrate computers, processors or ALUs into flexible fabrics that can be reused in various types of products. It remains to be seen whether these innovations can fulfil their promises. Anyway, if we look at the topology of these innovations, they have interesting similarities with gate array ASICs. The circle seems to be closing.

The introduction part of this thesis is organised as follows. Chapter 2 briefly introduces the design methods for IC-based systems; Chapter 3 introduces the main design problems the system architect has to face when developing complex systems; Chapter 4 presents the main ideas of the original papers in a condensed form; Chapter 5 introduces the original papers; and Chapter 6 gives the conclusions.

# 2. Design methods for IC-based systems

Integrated circuit technology has provided a variety of implementation formats for system designers. Implementation format defines what technology is used, how the switching elements are organised on the surface of chip and how the system functionality will be implemented. The implementation format also affects how systems are designed and limits the system complexity. Examples of the alternatives are a combinational logic implemented with discrete components and a billion-transistor Network-on-Chip consisting of tens of computers.

The integrated circuit technology has mostly been based on silicon. Today the majority of IC-based systems are based on CMOS technology (IC Insights 2001). The CMOS switching elements that implement basic Boolean functions such as AND, OR and NOT in the digital systems are the dominant technology. The current trend is to use Silicon-on-Insulator (SOI) technology to improve the circuit speed and power efficiency. However, the bipolar technology is widely used in analogue devices, BiCMOS technology is used in mixed-signal and microprocessor designs, and Gallium-Arsenide and Silicon-Germanium-based products are used in high-performance products.

If we look at the organisation of switching elements, regularity of organisation and granularity of elements are the essential parameters. Examples of regular formats are gate arrays, programmable logic devices (PLD), memories, field programmable gate arrays (FPGA), reconfigurable data path arrays (RDPA), and vector processors. Regularity has a strong impact on the required design effort, because the reuse of the design is very simple. The problems with regularity are that the usability and performance of resources may be limited because of the structure. The granularity expresses how much functionality is encapsulated into one design object. In fine-grain, medium-grain and coarse-grain formats the examples of basic units are the logic gates, standard cells – such as arithmetic logic units (ALUs) or multipliers – and intellectual property blocks – such as processor cores, network interfaces, etc. – respectively. The granularity affects the number of required design objects and, thereby, the required design or integration effort.

The three main approaches for implementing the system functionality are dedicated systems, reconfigurable systems and programmable systems. The

differentiating factor is the configuration frequency, i.e. how often the structure of the system is changed. In dedicated systems the structure is fixed at the design time, as in ASICs. In programmable systems the data path of the processor core, for example, is configured by every instruction fetched from memory during the decode-phase. The traditional microprocessor-based computer is the classical example. In the reconfigurable systems the structure of the system can be altered by changing the configuration data, as in field programmable gate arrays (FPGA). In dynamically reconfigurable systems the configuration can be done during run-time; in statically reconfigurable systems the configuration is done off-line

# 2.1 Basic blocks of integrated computers

The basic building blocks for application domain-specific integrated computers are input, output, data path, memory and control – as with an ordinary computer (Patterson & Hennessy 1998). The implementation format of each basic block can, at least theoretically, be any combination of the previous classes. For example, the data path and control can be implemented using fixed dedicated hardware, as in ASICs (Smith 1997), or reconfigurable logic (Caspi et al. 2001, Compton & Hauck 2002) or microprogrammed units, as in processors (Anceau 1986). The data path can consist of regular elements, as in reconfigurable arrays, or dedicated, pipelined blocks, as in superscalar processors. The granularity of data path elements can vary from single gates in ASIC to complete processors in multiprocessor architectures. However, an integrated computer system typically consists of a processor or processors, memory organisation and communication network. The tasks of the system architect are to know them, to identify the best alternatives and to join them, so that the system fulfilling the quality targets can be quantified and designed.

The diversity of the applications has led to a variety of processor architectures that exploit parallelism differently (Forsell 2002a). The basic taxonomy of processor architecture was presented by Flynn (1966) and used the number of instruction streams and data elements being processed as the criteria. Skillicorn (1988) extended Flynn's taxonomy to multiprocessor architectures and took into account the internal structure of the processor, e.g. pipelining and parallelism. Corporaal (1998) used the instruction issue rate, number of operations per

instruction, number of data elements in each operation and degree of superpipelining as the dimensions of the architecture design space.

The first microprocessors were sequential processors based on Von Neuman architecture (Mazor 1995). Initially, the lack of processor-memory bandwidth and poor compilers resulted in complex instruction sets, and they were called complex instruction set computers, CISC. In the early 1980s the invention of reduced instruction set architecture, RISC, and the development of VLSI technology enabled the implementation of a pipelined architecture, larger register banks and more address space in a single chip processor. In the 1990s the focus was on the exploitation of instruction-level parallelism, ILP, which eventually resulted in the modern general-purpose processors (Slater 1996). Superscalar and very long instruction word architectures, VLIW, are examples of dynamic and static parallelism. Data-level parallelism, DLP, has been exploited in instruction set extensions such as Intel's MMX and Sun's VIS, where the objective has been to improve the performance of multimedia applications. Recently the silicon capacity has enabled the implementation of the first microprocessors that exploit thread-level parallelism, TLP (Koufaty & Marr 2003), and process-level parallelism, PLP, where several processor cores are integrated into a single chip. OMAP processors from Texas Instruments are well-known examples. Research approaches that are even more complex have been proposed by Taylor et al. (2002) and Mai et al. (2000).

Another dimension in processor architectures has been the application orientation that has led to a variety of different types of instruction sets and organisations. Today, in addition to *general-purpose processors*, we also have *microcontrollers*, in which the memory organisation and peripherals are integrated into the same chip. *Digital signal processors* were invented to perform simple stream-based processing, such as filtering. The Harvard and SuperHarvard architectures, advanced addressing, efficient interfaces, and powerful functional units such as multiplier and barrel shifters give superior performance in the limited application space (Madisetti 1995). *Multimedia processors* are targeted at applications where data parallelism can be exploited efficiently, i.e. real-time compression and decompression of audio and video streams and generation of computer graphics. Multimedia processors can be divided into microprocessors with multimedia instruction extensions and highly parallel DSP processors (Kuroda & Nishitani 1998). *Network processors* have an

effective interconnection network between the processing elements that operate in parallel and efficient instructions for packet classification (Wolf & Turner 2001). *Reconfigurable data path arrays*, RDPAs, have coarse-grain functional units, such as ALUs or multipliers, as configurable elements (Hartenstein et al. 1996). Bondalapati & Prasanna (2002) and Compton & Hauck (2002) give extensive overviews of configurable systems, technologies and use.

Customisation of instruction set is another technique for improving the performance of a processor in a specific application domain. Coprocessors are hardware accelerators for specific types of applications, such as floating-point arithmetic or multimedia. In the reconfigurable coprocessors and reconfigurable computers the idea is to dynamically load the instruction into an FPGA block (Mangione-Smith et al. 1997). Configurable processors are targeted at Systemon-Chip products. The idea is that the processor's instructions are optimised for the application during the SoC design. The basic architecture is typically a pipelined RISC architecture, and new instructions are either integrated into the pipeline or implemented as coprocessors or architectural extensions (Wang et al. 2001, Campi et al. 2001). Application specific instruction processors, ASIP are designed for a particular application set. The idea is that the complete instruction set, and the selection of the architecture template, is based on the application analyses (Jain et al. 2001, Itoh et al. 2000). Application specific processors are processors that are synthesised from the application description using a built-in architecture template of the synthesis system. The idea is to extract computation resources from the application description and to synthesise the control that minimised the resources within given performance constraints (De Man et al. 1990).

Memory can be characterised with size, number of ports, latency and bandwidth. *Latency* is the access delay of a randomly chosen data element and *bandwidth* is the data rate of the elements. Semiconductor memory components are typically 2-dimensional regular structures, and latency is inversely proportional to the size of memory. The bandwidth depends on the memory buses, internal organisation of memory and access logic.

Computer memory is typically composed of hierarchically organised memory components or blocks. The levels of the hierarchy are called *layers*. The faster and more expensive memories are in the upper layers; the slower, bigger and

cheaper memories are in the lower layers. The objective is to keep the most accessed data items at the top of the hierarchy (Patterson & Hennessy 1998). Cache memories are fast memories between processors and the main memories that keep the most frequently used data items easily accessible. The idea is to benefit from spatial and temporal locality of memory accesses. Smith (1982) gives a good overview of cache memories. Virtual memory is a technique that implements the translation of a program's address space to a physical address space (Killburn et al. 1962). The benefits are that separately compiled programs can share the same memory and that by moving code and data between the main memory and the secondary storage a single program can exceed the physical address space (Jacob & Mudge 1998). Shared memories can be accessed by more than one processor in a multiprocessor system.

The main memory classes are volatile memories, e.g. static random access memory, SRAM, dynamic random access memory, DRAM, and non-volatile memories, such as read-only memory, ROM, and FLASH memory. SRAM is a fast memory, but typical implementation takes six transistors per bit. DRAM is a dense memory, only one transistor per bit, but the latency, e.g. access delay, is high. The FLASH memory also suffers from high latencies – the writing takes time, because it must be done for large blocks (Bez et al. 2003). The DRAM and FLASH memories are internally asynchronous and have different latencies for random and sequential accesses. For DRAM in particular, this has led to a variety of solutions for speeding up the overall performance, such as fast page mode accesses, synchronous interfaces, and intelligent control interfaces (Cuppu et al. 1999).

The design of memory organisation for an integrated computer system using *embedded memories* differs from a component-based memory system, because it is possible to change the parameters of the blocks, such as bus widths and memory capacity (Panda et al. 1999). The number of memory blocks does not cause a significant price increase, as is the case with discrete memory components. Only the total area is significant, because the design is relatively simple due to the regular structures of memories. Therefore, it is possible to divide the memory into smaller blocks according to the application requirements and architecture characteristics (Panda et al. 2001). The size of the memory blocks is very simple to change, making it possible to optimise the total area. The communication inside the chip is fast, which means that it is often possible

to simplify the memory organisation by reducing the number of layers. Removing caches or replacing them with *scratchpad* memories, for example, also improves power efficiency and simplifies the memory management units (Banakar et al. 2002). It is also possible to use wide buses and exploit data parallelism in communication as it is done between the cache and main memories.

Communication network is the third main component of a computer system. Communication channels can be divided into dedicated channels, e.g. *signals*, and shared channels, e.g. buses and networks. The *buses* connect subsystems, and *networks* connect computers according to the classical definition. The dedicated channels may be static *point-to-point* connections or dynamic *switched* connections. However, these distinctions are becoming very difficult with advanced buses and interconnect networks in multicomputer ASICs.

The buses can be further divided into CPU-memory and I/O buses, parallel and serial buses, or synchronous and asynchronous buses, according to their purpose or physical implementation. A typical personal computer has a CPU-memory bus that connects the cache and main memory, a high-speed bus for graphics processing, a peripheral bus and an I/O bus for external devices. The *bus transaction* is the basic read or write operation in the bus. The *bus master* is the component that can initiate transactions. The *bus slave* is the passive counterpart. In the case of multiple masters, the *bus arbiter* controls which one gets the bus. Several techniques, such as split transactions, pipelining and packet-switched buses, have been proposed for improving bus efficiency. The basics of buses, the main components and principles of operation are explained in more detail by Hennessy & Patterson (2003).

The AMBA bus is a typical example of a System-on-Chip bus. It consists of a high-speed bus for the CPU-memory interface and a low-speed peripheral bus for other, less demanding blocks (ARM 1999). Virtual Socket Interface Alliance has developed a standard interface for virtual components to on-chip buses, but real buses must be adapted to this interface with glue logic (Lennard et al. 2000). The MicroNetwork approach uses concurrent protocols, scalable data path widths and pipelining for decoupling the IP block design from the communication design (Wingard 2001). Lahtinen et al. (2002) distributes the arbitration among the connected agents. The approach is especially suitable for

continuous media systems. As examples of more complex buses, Leijten et al. (1998) have proposed a communication architecture that consists of FIFOs and time-multiplexed switches, and Lahiri et al. (2001) have introduced a randomised arbitration approach that improves bus performance. Salminen et al. (2002) gives an overview of System-on-Chip buses.

In some single-chip computer systems crossbar-switches and multistage interconnection networks based on packet-based messaging networks have replaced buses as communication channels. Interconnection networks originate from parallel supercomputer systems. Culler & Pal Singh (1999) give an introduction to the concepts, Sivaram et al. (2002) introduce taxonomy to switch architectures and Duato et al. (1997) describe the network topologies and networking principles in more detail. Dally & Towles (2001) have proposed onchip interconnection networks instead of top-level wiring of ASICs. The idea is partitioning of the chip area into tiles and network and increasing the modularity and the efficiency of the system. The basic topology is 2-dimensional mesh with buffered routers and processing tiles. Guerrier & Greiner (2000) presented a generic packet-switched interconnection template for on-chip communication and assessed its feasibility with regard to cost and performance. The basic topology is fat-tree and the router is based on a partial crossbar with input buffers and shared output buffers. A multitude of Network-on-Chip related architectures have been published since these early papers (Karim et al. 2002, Benini & De Micheli 2002, Sgroi et al. 2001, Saastamoinen et al. 2002, Wielage & Goossens 2002.). Jantsch & Tenhunen (2003) summarise the main results.

Today, the integrated computers are eventually manufactured in ASIC foundries using silicon-processing technology. This applies to System-on-Chip solutions, FPGA-based devices and reconfigurable data path arrays, and, most likely, it will apply to Networks-on-Chip. This leads to two main requirements for system architecture and design methodology. First, it must be possible to implement all the building blocks with the chosen process. This means that we have to be able to use the technologies, such as, for example, DRAM memories and FPGAs, as part of the ASIC manufacturing process. Second, we have to be able to design the complete system. This means that we have to be able combine the information from different areas such as algorithm design, software design, hardware design, so that decision making at the system level is possible.

## 2.2 Models and languages

The purpose of the design is to convert the user's requirements into a system that fulfils those requirements. In order to perform this task we need to have models of the system at different levels of details, i. e. abstraction levels, and languages that describe the contents of those models. The design process is basically a sequence of steps that takes a model of a design at a higher level and transforms or refines it into a lower level model, so it consists of both models and methods. At every abstraction level we have a model that is based on a language consisting of syntax and semantics. The model of computation defines how the abstract machine can behave in operational semantics. It is important to notice that one language can contain several models of computation, and one model can have parts described in different languages.

Edwards et al. (1997) define the most common models of computation used in embedded systems.

- Discrete event models are based on the idea that tokens or events carry a totally ordered time stamp, as in VHDL simulation. The major problem is non-determinism in case of simultaneous events.

- Communicating Sequential Processes were proposed by Hoare (1985). Harel (1987) introduced hierarchy, concurrency and non-determinism into traditional finite state machines. Finite State Machine-based languages have been used by Balarin et al. (1997).

- The synchronous and reactive models (Berry & Gonthier 1992) are based on the idea that all signal event pairs are totally ordered and globally available, as in cycle-based simulators where all the values of signals are evaluated at every clock cycle.

- Dataflow Process Networks (Lee & Parks 1995) describes the systems as directed graphs where computation occurs in nodes, communication happens via arcs, and events and data are presented as tokens.

Other models of computation include rendezvous-based models that are used in process calculus. Lee & Sangiovanni-Vincentelli (1998) have proposed a

framework for comparing models of computation in the form of a meta-model. The goal is to enable transformation between modelling languages, which is needed in system synthesis from heterogeneous specification. Gajski et al. (1994) presented a model taxonomy for codesign methods, which divided models into state-oriented models, activity-oriented models, structure-oriented models, data-oriented models and heterogeneous models. The RASSP taxonomy targeted mainly at DSP systems used temporal, data value, functional and structural resolutions and programming level as classification criteria (Hein et al. 1997).

The abstraction levels and design domains have developed with the ability to use more abstract design methods and new technologies. The Y-chart by Gajski (1988) divided system models into behavioural, structural and physical domains, which each had five abstraction levels: system level, algorithm level, microarchitecture level, logic level and gate level. Later, Gajski et al. (1996) refined the levels more suitable for Systems-on-Chip. The new levels were processor level, register level, gate level and transistor level. The D-cube classification by Ecker (1995) divides the systems according to views, values and timing. The view can be sequential, concurrent or structural. The values can be abstract, composite or bits. The timing can be based on causality, clocking or propagation delays. The RASSP project collected and classified the most used techniques in the DSP domain; the subsystem's hierarchy and emphasising performance issues were the main enhancements (Hein et al. 1997).

There is a lot of variety in abstraction levels, design domains and design tasks in the design of a complex integrated multiprocessor system. This has led to a variety of languages for different purposes. The languages targeted at the modelling of complete systems are very difficult to classify according to traditional classification criteria. Therefore, only a brief introduction to the most important language classes is given.

Formats are used for presenting design information. CIF (Caltech Intermediate Format) and GDSII Stream are formats used for presenting the final layout of the ASIC. EDIF (Electronic design interchange format) is used for presenting design data such as netlist, so that it can be transferred between design environments and design tools. The CAD framework initiative, CFI, has defined a standard for

design representation, which is based on an information model for electrical connectivity information. (Smith 1997)

Hardware description languages (HDL) can be roughly divided into structural languages that replaced the schematic entries and behavioural languages that are used as higher abstraction level inputs for synthesis tools or simulation tools. VHDL and Verilog are currently the most used languages and include features of both classes (Smith 1997). Using C and, currently, C++ as a basic of HDL has been considered an attractive alternative and has generated a variety of languages, such as HardwareC (Gupta & De Micheli 1993) and SystemC (Grötker et al. 2002). Architecture description languages (Bashford et al. 1994, Fauth et al. 1995, Pees et al. 1999) are a special case of HDLs. They have been targeted at the modelling of computer and processor architectures.

Software languages were developed for easing up the program development. The microprogramming languages define how the processor is configured during the execution of an instruction. The machine code is the sequence of instructions executed by the processor. The programming languages or high level languages, such as ALGOL, Fortran, Basic or C, are transformed into machine code by compilers or interpreters (Aho et al. 1986). In Java language, the whole computer is emulated by a virtual machine program.

Specification and modelling languages are targeted at design capture instead of implementation description. Data flow process networks have been widely used in digital signal processing systems (Lee & Parks 1995). The actual content of the processes has been modelled with host languages like Prism or C. Formal specification languages, such as Synchronized Transitions, Unity and LOTOS, enable mechanical model checking of system properties. System-level design languages (Bahill et al. 1998) are used for creating high-level abstraction of the desired system. Unified Modelling Language, UML is an attempt to combine different approaches under one framework (Fowler & Scott 1997).

# 2.3 Design flows

Every product consists of two parts – functionality and physical realisation, e.g. resources – and the design flow is a process in which the system requirements

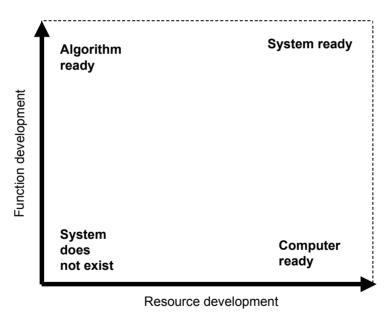

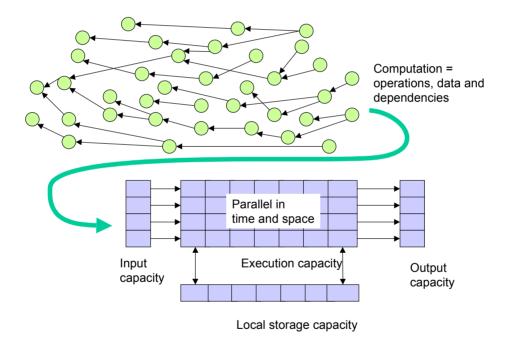

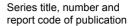

related to these parts are transformed into a product fulfilling them. In the process the designer adds implementation details to a system model until the product is designed. These additions concern either functionality or resources, as depicted in Figure 2. The design flow can then be considered a path on a plane, from a point where no implementation details exist to the point where the product's implementation is fully specified.

The optimal design flow depends on various aspects, including technologies, design tools, business strategies, and market situation. The design flows for mass-market products emphasise optimisation of manufacturing and material costs, which are mostly dependent on resource optimisation. The competitive advantages of high-end products are often related to functional performance. In these cases the management of functional complexity, advanced algorithms and performance benefits via optimisations of functionality are critical. In emerging markets the time-to-market issues are important and the emphasis is, therefore, on the reuse of existing knowledge and parallel development of new features.

Figure 2. Design plane concept.

The IC-based systems can be roughly divided into three classes: ASICs, computers-based systems and System-on-Chips. The ASICs are mainly dedicated hardware implementations of algorithms, e.g. algorithm-on-chip-type

systems. The algorithm design precedes the resource design in the design flow. The computer-based systems are embedded system-type designs and the generic resources are designed before the actual functionality is implemented using software. In the System-on-Chip design the idea is find the optimal balance between the two earlier approaches. In practice this means the implementation of independent models and system-level optimisation criteria during architecture definition.

# 2.3.1 Dedicated hardware systems

ASICs are, by definition, applications implemented as integrated circuits. Designing and implementing an ASIC is an expensive and time-consuming process. It typically takes from 6 to 18 months to complete and the mask costs of an advanced manufacturing process alone are several hundred thousand Euros. A characteristic feature of an ASIC is that design mistakes or errors cannot be corrected from the final chip. Redesign and a new manufacturing iteration are required instead, taking at least one month to complete. Therefore, validation of the system functionality and verification of the design is extremely important. (Smith 1997)

## Specification of functionality and algorithms

The dedicated hardware system design starts from definition and validation of functionality. In most of the design flows the design of functionality is separated from the design of implementation, e.g. resources and their control. The motivation has been the separation of concerns. Functionality has been considered independently of implementation and, therefore, has been modelled and validated using methods that are specific to the types of systems. The state-based models and algorithms are the two most common classes of functional specifications. In reactive systems the state-based approaches are more common because it is easier to model the input-output responses and internal states of a system. In the case of data manipulation, the algorithmic approaches are more natural.

The quality of the functional description depends on the functional correctness, refinement process and complexity. Functional simulation is the most common

approach for the validation of correctness, but formal approaches have also been proposed. Functional correctness is especially important in the case of dedicated hardware implementation, because of the extremely high cost of redesign and manufacturing. The main problem with simulation-based validation is simulation coverage. The state-space explosion problem is especially significant in user interfaces and reactive products. The number of use cases or use scenarios can easily exceed any simulation capacity. Formal approaches, such as state reachability analysis and property checking, have been applied to life-critical systems because they provide complete coverage and certainty, but the cost of use, e.g. the modelling effort, is high.

The functional specification itself may contain several abstraction levels, from pure behaviour to implementable behaviour, and the design flow must support this refinement process so that the final implementation complexity can be minimised. For example, in digital signal processing systems the design typically starts from mathematical models, e.g. sets of equations. Then they are partitioned into modules that are described using algorithms and real numbers, e.g. floating point arithmetic. These algorithms are validated using functional simulations. However, the implementation is normally much cheaper if the total cost function, which has number of bits in data, number of operations between data, the required storage for data, and the control of operations as the main factors, is minimised. Part of this minimisation must be done in the functional specification. For example, the number of bits can be affected by the selection of number system and by scaling. The effects of these decisions must be modelled in a fixed-point model and validated by simulations.

## ASIC design

The ASIC design itself means the development of resources that implement the desired functionality. The ASIC design flow consists of *logical design* comprising design entry, netlist generation, system partitioning, logic simulation – and *physical design* – comprising floorplanning, placement, routing, circuit extraction and post-layout simulations (Smith 1997). The design entry contains the architecture design activities in this model, netlist generation refers to logic synthesis, and system partitioning refers to partitioning the system into different ASICs. The actual tools and design methods that have been used in various

phases changed with the advances in the EDA industry, from hand design to behavioural synthesis and formal verification (MacMillen et al. 2000).

Current ASIC design flows are based on synthesis. The input to synthesis is either a behavioural or RTL-level HDL description of the system. These approaches are called behavioural synthesis and logic synthesis respectively. The result of behavioural synthesis is RTL-level description, which must then be synthesised using logic synthesis. Behavioural synthesis, also called high-level synthesis, comprises the compilation, transformation, scheduling, allocation, partitioning and output generation phases (Walker & Camposano 1991, Gajski 1988). Compilation generates an internal presentation from the source language. Transformations are compiler optimisations or hardware-specific optimisations that try to optimise the behaviour of the design. The scheduling assigns operations to a point in time that is a control step in case of synchronous design. The allocation can be divided into register allocation, function allocation and interconnection binding. The idea is to define what resources are used for the execution of operations, and how to control the execution. It is mostly resolved using graph-theoretical methods. In order to process the design more efficiently it may be feasible to partition it into smaller, independent pieces. This can be done in various phases of the synthesis process. Output generation generates the RTL description for logic synthesis. Logic synthesis consists of translations and optimisations, but the output of synthesis is mostly determined by the coding style (Kurup & Abbasi 1997, Keating & Bricaud 1999). The basic flow is that the HDL is first translated to a network of generic logic cells that are technology independent. Second, the generic network is optimised using logic optimisation techniques; the optimisation is controlled by design constraints given by the user. Finally, the generic cells are mapped to cells from the target library that is technology-dependent. The optimisation goal in synthesis tools has been to meet timing constraints while minimising the area that is the main cost factor in ASICs. Advanced scheduling and allocation techniques, more complex library components, static timing analysis and timing-driven optimisations at the generic netlist level have been used for achieving these objectives. The current challenge in synthesis is taking the interconnect delay into account. The timing estimation has been based on gate delays and average wiring delays, but with shrinking feature sizes, interconnect delays are so dominating that average models are not accurate enough. *Physical synthesis* approaches try to solve these problems.

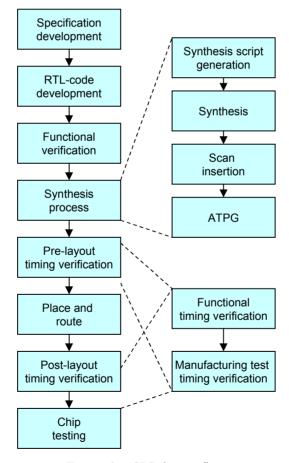

Figure 3 depicts the activities needed in ASIC design flow. The physical design and verification are the most time-consuming activities. Physical design, which is also called layout synthesis, is largely done using automated tools. However, there have recently been attempts to integrate the physical design and synthesis tools in order to manage the timing closure problems better (Chan et al. 2003). The verification consists of two parts: verification of design, which is done using simulation and formal methods, and verification of implementation, which means the design of tests – e.g. automated test pattern generation (ATPG) – and design for testability – e.g. insertion of scan structures and test ports. Current hardware simulators create native language executables, use event-based and cycle-based simulations, and support external executable models and hardware acceleration.

Figure 3. ASIC design flow.

In dedicated hardware design flow the functionality is designed before the resources. Only minor changes to functionality are possible when a typical industrial ASIC design is started. The fixed-point model design in digital signal processing is one example where this kind of optimisation is possible. If we use the design space representation of Figure 2, the path goes from bottom-left corner to top-left and from there to top-right.

## 2.3.2 Computer-based system design

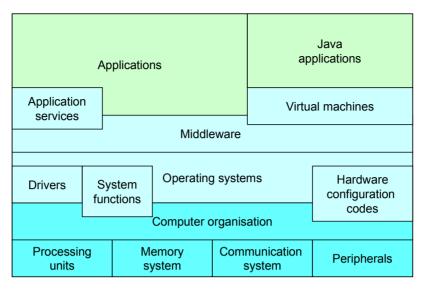

The computer-based systems consist of computer hardware, software environment and applications as depicted in Figure 4. The design flow of computer-based systems has two distinct phases. Before the actual functionality of the system can be designed, we have to have an existing computer and software development tools and an environment for software. Typically, the computers are not designed with a single application in mind. Instead, the objective is to provide computation and storage capacity for a set of applications. The application set can be anything between arbitrary functions to a set of few predefined functions only, but in general, the computer design aims at providing generic resources for various types of systems. Naturally, the benefit is to be able to reuse the hardware design in several products and thereby improve the design productivity.

The same objectives have also affected software development. First, the high-level programming languages and compilers divided the software development into coding and compilation that were processor-independent and dependent respectively. Second, the operating systems encapsulated hardware-related functionalities into system services that could be called from the applications. The result was that application development became computer-independent. Recently, the Java virtual machine has moved the abstraction level even higher; the application can be developed without knowing anything about the actual implementation of the hardware or software platform.

Figure 4. Basic structure of a computer-based system.

The cost of using existing hardware and software platforms is the implementation overheads. The economical and physical constraints are difficult to meet. Therefore, the choice of reuse level is an important design decision.

#### Designing computer resources

In the computer design the problems are to understand which design attributes are important and to maximise the performance and power efficiency under the design constraints. This process is covered in detail by Hennessy & Patterson (2003). The main activities are instruction set design, functional organisation – e.g. memory system design, processor design, bus architecture, I/O system design – logic design and implementation.

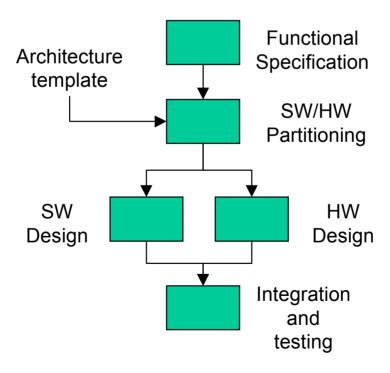

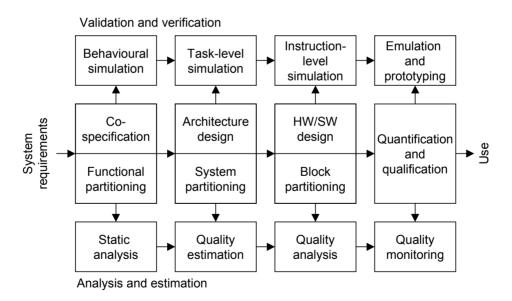

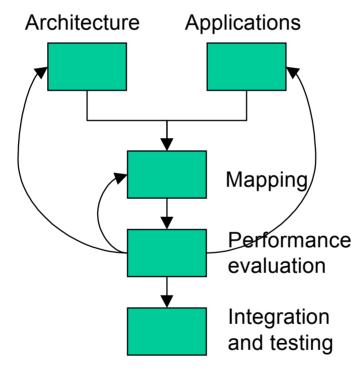

The actual design flow and tools naturally depend on the degree of freedom we have. However, the generic principle is that first the characteristic features of the application domain are analysed and the model of the workload is generated. Second, the system model is implemented and the workload is mapped to it. Third, the quality characteristics of the system are evaluated; in the case of the computers, the performance has been considered most important. Fourth, the system model is refined until a satisfactory quality is reached. The process is then repeated with a more detailed system model until the implementation exists.

If it is possible to change the internal structure of the processor, there are lot of design alternatives. In addition to the instruction set architecture – e.g. basic architecture style, memory addressing, operands, operations and control flow issues – pipelining and parallelism must also be studied in order to maximise the performance and resource utilisation. The most important objectives are "to make the common case fast", to benefit from overlapping of instructions. In addition to the hardware, compatibility and software development must also be considered. The processor design typically starts with analytical modelling, analysis and performance simulation. Several architecture languages and simulation environments have also been developed (Bashford et al. 1994, Fauth et al. 1995, Pees et al. 1999).

If we are limited to modifying the processor instruction set or memory organisation, a better understanding of the application domain becomes more important. In the case of processors, the profiling and identification of the critical functions are techniques that can help in the optimisation of the instruction set. These are especially important in the case of application-specific instruction-set processors and reconfigurable processors (Wang et al. 2001). Instruction-set simulation is the validation technique used at this level. The analysis of the memory footprints and locality of data, and the modelling of memory bandwidth with analytical methods or trace-based simulations are tools for cache and main memory optimisation (Panda et al. 2001).

The role of performance analysis using simulation or monitoring with benchmark programs is important when the objective is to balance the system performance and identify possible bottlenecks, as in designing computers using existing components (Bose & Conte 1998). At this level the system model is constructed using the models of existing building blocks, and, instead of designing components, the focus is on the selection of components.

In all phases of computer design the evaluation of performance depends on the workload model. Therefore, the quality of the workload model is essential and workload modelling is a widely studied topic (John et al. 1998). The main problem is that the applications run by the end users are unknown and their characteristics are always more or less guesses. It has also been shown that typical workloads do not exist and the characteristics of different applications are contradictory.

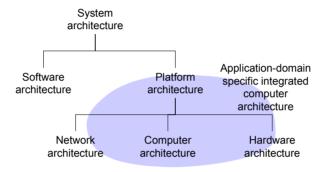

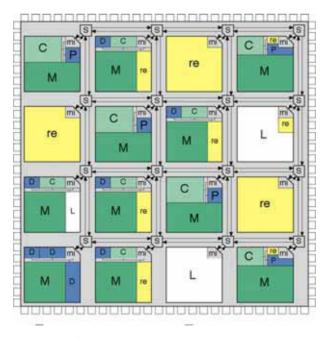

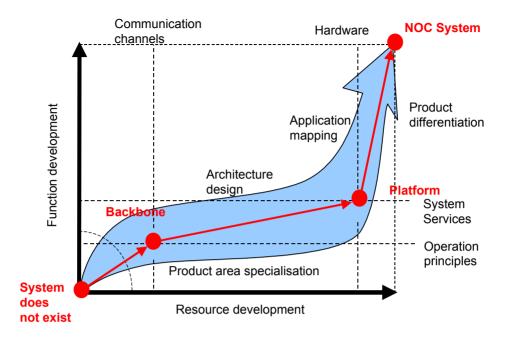

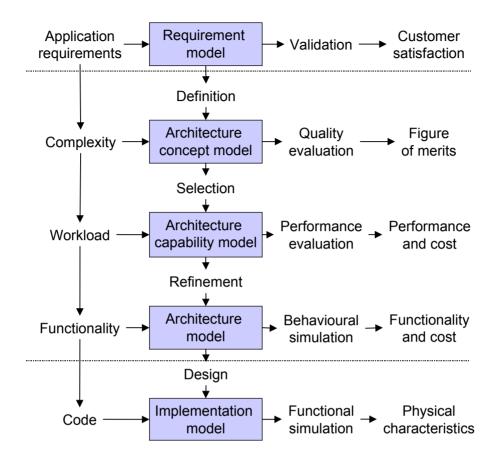

## Designing functionality as software