# The current state of FPGA technology in the nuclear domain

Jukka Ranta

**VTT TECHNOLOGY 10**

# The current state of FPGA technology in the nuclear domain

Jukka Ranta VTT

ISBN 978-951-38-7622-7 (URL: http://www.vtt.fi/publications/index.jsp) ISSN 2242-122X (URL: http://www.vtt.fi/publications/index.jsp)

Copyright © VTT 2012

JULKAISIJA – UTGIVARE – PUBLISHER VTT PL 1000 (Vuorimiehentie 5, Espoo) 02044 VTT Puh. 020 722 111, faksi 020 722 4374

VTT PB 1000 (Bergsmansvägen 5, Esbo) FI-2044 VTT Tfn +358 20 722 111, telefax +358 20 722 4374

VTT Technical Research Centre of Finland P.O. Box 1000 (Vuorimiehentie 5, Espoo) FI-02044 VTT, Finland Tel. +358 20 722 111, fax + 358 20 722 4374

#### The current state of FPGA technology in the nuclear domain

Jukka Ranta. Espoo 2012. VTT Technology 10. 62 p.

# Abstract

Field programmable gate arrays are a form of programmable electronic device used in various applications including automation systems. In recent years, there has been a growing interest in the use of FPGA-based systems also for safety automation of nuclear power plants. The interest is driven by the need for reliable new alternatives to replace, on one hand, the aging technology currently in use and, on the other hand, microprocessor and software-based systems, which are seen as overly complex from the safety evaluation point of view.

This report presents an overview of FPGA technology, including hardware aspects, the application development process, risks and advantages of the technology, and introduces some of the current systems.

FPGAs contain an interesting combination of features from software-based and fully hardware-based systems. Application development has a great deal in common with software development, but the final product is a hardware component without the operating system and other platform functions on which software would execute.

Currently the number of FPGA-based applications used for safety functions of nuclear power plants is rather limited, but it is growing. So far there is little experience or common solid understanding between different parties on how FPGAs should be evaluated and handled in the licensing process.

Keywords nuclear power, instrumentation and control, I&C, FPGA

# Preface

This report has been prepared as a part of the Coverage and Rationality of the Software I&C Safety Assurance (CORSICA) project. CORSICA is a part of the Finnish Research Programme on Nuclear Power Plant Safety 2011–2014 (SAFIR2014).

The goal of the project was to survey field programmable gate array (FPGA) technology and the situation of its use in nuclear power generation. FPGA technology has become a topic of interest as a potential technology suitable for the safety-critical I&C systems of nuclear power plants. The primary task was to collect an information package that can serve the interested parties, including utilities and regulators, when considering FPGA-based systems offered for use in Finnish nuclear power plants. In addition to the technology as such, the risks, advantages and special characteristics were also to be considered.

Espoo, December 2011

# Contents

| Ab  | stract       |                                                      | 3  |

|-----|--------------|------------------------------------------------------|----|

| Pre | eface.       |                                                      | 4  |

| Lis | t of sy      | /mbols                                               | 7  |

| 1.  | Introduction |                                                      |    |

|     |              |                                                      |    |

| 2.  |              | A technology – hardware aspects                      |    |

|     | 2.1          | CMOS.                                                |    |

|     | 2.2          | Chip architecture                                    |    |

|     | 2.3          | Antifuse, SRAM, and flash technologies               |    |

|     | 2.4          | Circuit board and connections                        |    |

|     | 2.5          | Electrical and mechanical properties and reliability |    |

|     |              | 2.5.1 Faults                                         |    |

|     |              | 2.5.2 Environmental tolerance                        |    |

|     |              | 2.5.3 Aging                                          |    |

|     |              | 2.5.4 Whisker growth                                 |    |

|     |              | 2.5.5 Radiation dose and single event effects        |    |

|     |              | 2.5.6 Current leakage                                |    |

|     |              | 2.5.7 Latchup                                        |    |

|     | ~ ~          | 2.5.8 Manufacturing technology size scale            |    |

|     | 2.6          | Timing, clock skew, and race condition               |    |

|     | 2.7          | Metastability                                        |    |

|     | 2.8          | Parallel computing                                   |    |

|     | 2.9          | System on a chip – SOC                               |    |

|     | 2.10         | FPAA – a glimpse of analog technology                | 22 |

| 3.  | Appl         | ication design and development                       | 23 |

|     | 3.1          | Design life cycle, stages, and work flow             |    |

|     | 3.2          | Requirements specification                           |    |

|     |              | 3.2.1 ESL – electronic system level                  |    |

|     | 3.3          | V&V: requirements                                    |    |

|     | 3.4          | Architectural design                                 |    |

|     | 3.5          | Detailed design                                      |    |

|     | 3.6          | V&V: architectural and detailed design               |    |

|     | 3.7          | Behavioural description and design entry             |    |

|     |              | 3.7.1 Hardware description languages – HDL           |    |

|     |              | 3.7.2 Higher-level entry methods                     |    |

|     |              | 3.7.3 Other entry methods                            |    |

|     | 3.8          | Intellectual property – IP cores                     |    |

|     | 3.9          | V&V: design entry                                    |    |

|     |              | Implementation: logic synthesis and place and route  |    |

|     | 3.11         | V&V: logic synthesis and place and route             | 31 |

|    | 3.12   | Implementation: configuring a chip and putting a programmed chip    | 20 |

|----|--------|---------------------------------------------------------------------|----|

|    | 2 4 2  | onto a board<br>V&V: physical implementation                        |    |

|    |        | Other verification and validation issues                            |    |

|    | 5.14   | 3.14.1 Importance of independent V&V                                |    |

|    |        | 3.14.2 Formal methods                                               |    |

|    | 3 15   | Tools                                                               |    |

|    |        | Emulated processor                                                  |    |

|    |        | Timing analysis                                                     |    |

|    |        | Synchronous vs. asynchronous design                                 |    |

|    |        | Hardware vs. software aspects of design                             |    |

|    |        | Standards                                                           |    |

| 4. | Risk   | s and advantages                                                    | 39 |

|    | 4.1    | Faults, tolerance, and mitigation                                   |    |

|    |        | 4.1.1 Triple modular redundancy                                     |    |

|    |        | 4.1.2 EDAC and hamming codes                                        |    |

|    |        | 4.1.3 Diversity                                                     |    |

|    | 4.2    | Advantages of FPGA technology                                       | 42 |

|    | 4.3    | Experience from other fields                                        | 44 |

|    | 4.4    | Security                                                            | 44 |

|    |        | 4.4.1 Problem areas                                                 | 44 |

|    |        | 4.4.2 Managing security problems                                    |    |

|    |        | 4.4.3 Attack methods                                                | 46 |

|    |        | 4.4.4 Defences                                                      | 47 |

| 5. | Curr   | ent systems                                                         | 48 |

|    | 5.1    | CANDU                                                               | 49 |

|    | 5.2    | Lungmen                                                             | 49 |

|    | 5.3    | Wolf Creek                                                          | 49 |

|    | 5.4    | RPC Radiy                                                           | 50 |

|    |        | 5.4.1 IERICS mission on FPGA-based digital I&C platform and systems | 51 |

|    | 5.5    | Rolls-Royce and Electricité de France                               |    |

|    | 5.6    | Toshiba                                                             |    |

| 6. | Sum    | mary                                                                |    |

| -  |        | •                                                                   |    |

| ке | rerend | ;es                                                                 | 55 |

# List of symbols

| ASIC                                                                    | Application Specific Integrated Circuit                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BiS                                                                     | Built-in Software                                                                                                                                                                                                                                                                                                                                         |

| BIST                                                                    | Built-in Self-test                                                                                                                                                                                                                                                                                                                                        |

| CAB                                                                     | Configurable Analog Block                                                                                                                                                                                                                                                                                                                                 |

| CCF                                                                     | Common Cause Failure                                                                                                                                                                                                                                                                                                                                      |

| CEC                                                                     | Complex Electronic Component                                                                                                                                                                                                                                                                                                                              |

| CLB                                                                     | Configurable Logic Block                                                                                                                                                                                                                                                                                                                                  |

| CMOS                                                                    | Complementary Metal Oxide Semiconductor                                                                                                                                                                                                                                                                                                                   |

| CPLD                                                                    | Complex Programmable Logic Device                                                                                                                                                                                                                                                                                                                         |

| CPU                                                                     | Central Processing Unit                                                                                                                                                                                                                                                                                                                                   |

| EDA                                                                     | Electronic Design Automation                                                                                                                                                                                                                                                                                                                              |

| EDAC                                                                    | Error Detection And Correction                                                                                                                                                                                                                                                                                                                            |

| EDIF                                                                    | Electronic Design Interchange Format                                                                                                                                                                                                                                                                                                                      |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                           |

| EEEPROM                                                                 | Electrically Erasable Programmable Read-Only Memory                                                                                                                                                                                                                                                                                                       |

| EEEPROM<br>EM                                                           | Electrically Erasable Programmable Read-Only Memory<br>Electromigration                                                                                                                                                                                                                                                                                   |

| -                                                                       |                                                                                                                                                                                                                                                                                                                                                           |

| EM                                                                      | Electromigration                                                                                                                                                                                                                                                                                                                                          |

| EM<br>EMC                                                               | Electromigration<br>Electromagnetic Compatibility                                                                                                                                                                                                                                                                                                         |

| EM<br>EMC<br>EPLD                                                       | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device                                                                                                                                                                                                                                                                   |

| EM<br>EMC<br>EPLD<br>EPROM                                              | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory                                                                                                                                                                                                                         |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL                                       | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level                                                                                                                                                                                              |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL<br>FPAA                               | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level<br>Field Programmable Analog Array                                                                                                                                                           |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL<br>FPAA<br>FPGA                       | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level<br>Field Programmable Analog Array<br>Field Programmable Gate Array                                                                                                                          |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL<br>FPAA<br>FPGA<br>HCI                | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level<br>Field Programmable Analog Array<br>Field Programmable Gate Array<br>Hot Carrier Injection                                                                                                 |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL<br>FPAA<br>FPGA<br>HCI<br>HDL         | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level<br>Field Programmable Analog Array<br>Field Programmable Gate Array<br>Hot Carrier Injection<br>Hardware Description (Definition) Language                                                   |

| EM<br>EMC<br>EPLD<br>EPROM<br>ESL<br>FPAA<br>FPGA<br>HCI<br>HDL<br>HDVL | Electromigration<br>Electromagnetic Compatibility<br>Erasable Programmable Logic Device<br>Erasable Programmable Read-Only Memory<br>Electronic System Level<br>Field Programmable Analog Array<br>Field Programmable Gate Array<br>Hot Carrier Injection<br>Hardware Description (Definition) Language<br>Hardware Description and Verification Language |

| I&C       | Instrumentation and Control                       |

|-----------|---------------------------------------------------|

| IAEA      | International Atomic Energy Agency                |

| IC        | Integrated Circuit                                |

| IDE       | Integrated Development Environment                |

| IP (Core) | Intellectual Property Core                        |

| LAB       | Logic Array Block                                 |

| LUT       | Look-Up Table                                     |

| MOSFET    | Metal Oxide Semiconductor Field-Effect Transistor |

| NBTI      | Negative Bias Temperature Instability             |

| NPP       | Nuclear Power Plant                               |

| P/E Cycle | Program/Erase Cycle                               |

| PCEC      | Programmable Complex Electronic Component         |

| PDED      | Pre-Developed Electronic Design                   |

| PDS       | Pre-Developed Software                            |

| PLD       | Programmable Logic Device (see also EPLD, CPLD)   |

| RTL       | Register Transfer Level                           |

| SEE       | Single Event Effect                               |

| SEFI      | Single Event Functional Interrupt                 |

| SEL       | Single Event Latch-up                             |

| SER       | Soft Error Rate                                   |

| SET       | Single Event Transient                            |

| SEU       | Single Event Upset                                |

| SoC       | System on Chip                                    |

| SOI       | Silicon On Insulator                              |

| SRAM      | Static Random Access Memory                       |

| STA       | Static Timing Analysis                            |

| TDDB      | Time Dependent Dielectric Breakdown               |

| TID       | Total Ionizing Dose                               |

| TMR       | Triple Modular Redundancy                         |

| V&V       | Verification and Validation                       |

| VHDL      | Very high speed integrated circuit (VHSIC) HDL    |

| VHSIC     | Very High Speed Integrated Circuit, see VHDL      |

| VLSI      | Very Large Scale Integration                      |

# 1. Introduction

Interest in the use of field programmable gate array (FPGA) technology in nuclear power plant (NPP) automation has increased in recent years. The technology is not new and is widely used in other areas. But it is new, in particular in safety-related systems, in NPPs. Old analog and micro-controller systems are becoming obsolete and need to be replaced. At the same time, decisions on the technology to be used in new plants need to be made. The experience of software-based systems is that demonstrating their reliability and safety in the licensing process is difficult and laborious. FPGAs are seen as an option that provides flexibility and capability similar to software but with the lower complexity, simpler system structure, and improved performance characteristic of hardware. There are other advantages to using FPGAs, but there are also risks involved. The suitability, reliability, and possible problems of licencing a novel technology in the nuclear power generation domain all have uncertainties.

FPGAs are just one of the new trends in instrumentation and control technology (I&C). See, for example, the survey reports prepared for the United States Nuclear Regulatory Commission (U.S. NRC) [NRC, 2003], [NRC, 2006] and [NRC, 2009a]. The FPGA-specific reports by the Electric Power Research Institute [EPRI, 2009, 2011] indicate a strong interest on behalf of the industry, while the review guide-lines document [NRC, 2010b] indicates the interest of regulators to prepare for increased use of FPGAs and similar technologies.

The FPGA device itself is a semiconductor silicon chip with a regular array of transistors. As such it has no functions. The device can be configured (programmed) for a task after manufacture by configuring the connections between the components on the chip. This allows standardised mass production of the devices independent of the applications for which they are intended. And this, in turn, provides advantages for the development process and manufacture.

The development of an FPGA application has strong similarities with software development. Both use rather high abstraction level programming/description languages and the design process is heavily dependent on software tools. The design of complex systems is easy, but verification of the correct functioning of those systems is not. A significant difference is that an FPGA application does not need an operating system, hardware drivers, or other similar platform. However, such a computing environment can be configured onto a device with sufficient

capacity. In addition, FPGAs use parallel processing with dedicated hardware for each function instead of executing a program one instruction at a time.

Reasons to use FPGAs include the hope for an easier licensing process compared to microprocessor and software-based alternatives. On the other hand, the simpler analog systems are becoming obsolete. FPGAs can provide fast response times with dedicated hardware for each task and reduced concerns about tasks interfering with each other. Cyber security issues are also considered to be less with FPGAs than with software, because an FPGA can contain all of the memory and functions and it is difficult, or impossible for certain technologies, to alter it, that is, make the device run viruses.

The risks associated with FPGAs and software-based systems have much in common. The correctness of the functioning may be difficult to prove due to complexity of the system and the layers of design tools between the requirements specification and the final product. Because the technology is new in the nuclear power generation industry, there is little experience of what it is most suited for or how it should be implemented.

Currently there are only a few licensed and operational FPGA-based systems performing safety-related functions at nuclear power plants. A rather large number of them are in Ukrainian and Bulgarian NPPs and were installed as parts of modernisation projects. Another major project is going on in France and also deals with modernisation. Mostly, the other developed applications are experimental and are intended for testing in a simulator and developing experience and expertise.

A standardisation process is underway to develop the IEC 62566 standard for use of hardware description language programmable devices in nuclear power plants. It is expected to be published in spring 2012. Due to the nature of FPGAs having a mixture of features from hardware and software, both types of standards can be relevant for licensing.

This report aims to give a basic overall working knowledge about FPGA technology. From this report, the reader should gain sufficient background information and readiness to access the more topically specialised literature. The main focus is on safety and reliability issues. In Chapter 2, physical technological aspects are considered. Chapter 3 presents the application design process and related issues. The reasons to use FPGA technology along with selected risks and security issues are considered in Chapter 4. Some FPGA-based systems in development or already in use are presented in Chapter 5. A summary is given in Chapter 6.

# 2. FPGA technology – hardware aspects

Field programmable gate arrays appeared on the market in the late 1980s. They are a step in the continuum of evolution of integrated circuits (IC). They are one of the programmable logic devices (PLD) and, due to their flexibility and capacity for various applications, are considered complex electronic components (CEC). Their strength is the idea of a functionally blank device with the potential to be configured for various implementations, thus allowing mass production of devices independent of the final application. An FPGA device can be programmed after manufacture to execute the desired logic or computations. The chip contains a large number of similar basic elements in a fixed structure. The programming is done by configuring these basic elements and the connections between them. The words programming and configuring are used interchangeably in the literature.

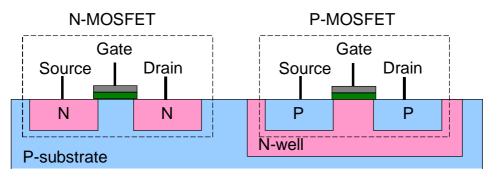

Physically, an FPGA chip is CMOS (complementary metal oxide semiconductor) technology, which is the most common technology in modern ICs. The fundamental components of CMOS are paired P- and N-type semiconductor transistors, which implement the logical gates. Functions are designed by configuring the wiring between the gates.

Technologically, the basics of FPGA have stayed the same and are the same as in most digital computing technology. The capacity, though, has increased tremendously. The amount of logical operations that a chip can contain, measured in the number of logical gates on the chip, has increased from a few thousand to millions. In addition, separate RAM memory and dedicated blocks for, for example, numerical computations or even microprocessors are available in the more advanced chips. This leads to the possibility of producing system on a chip (SOC) applications. SOC is something of a sliding concept but means that all functions (an entire computer) are on the same chip.

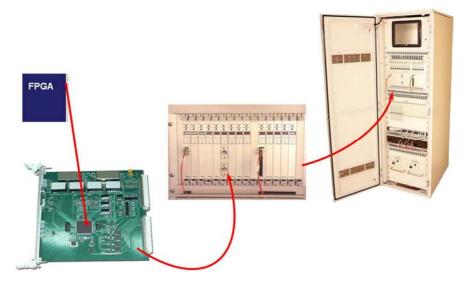

An FPGA application consists of the device (chip and packaging with contact pins), the circuit board, and the auxiliary hardware on the board. In addition, there are the cabinets to hold the boards and wiring for measurement signals, communication with other devices or instrumentation, and power. The board can also contain separate hardware for signal processing (e.g., conversion between analog and digital signals and filtering), input/output connectors, memory, and other processing units.

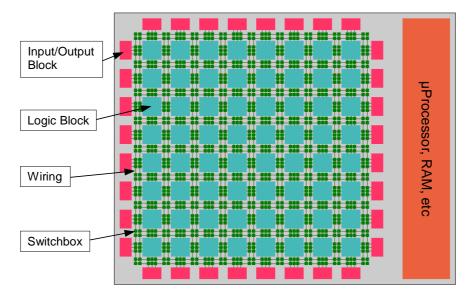

Architecturally, FPGAs consists of I/O blocks, logical gates which form configurable logic blocks (CLB), and the wiring between them. The logic blocks can execute simple logic themselves, such as a 4-input lookup table, and typically have flip-flops for memory. The switches of the wiring allow the connection of I/O blocks and logic blocks to generate more complex logic.

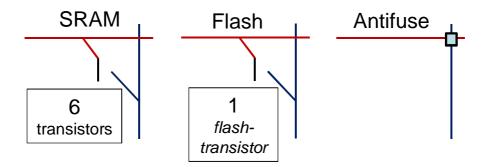

Three types of FPGA technology are available with regards to the programming technology. These are antifuse, SRAM, and flash. Each one stores the configuration in a different way, which affects the way the chip can be used and also the physical properties, such as aging and radiation tolerance. Aside from the programming technology, all three use CMOS technology to implement the actual logic operations.

A distinct difference between an FPGA application and a microprocessor application running software is in parallel computing. An FPGA executes all of the logic on each clock cycle, whereas a microprocessor executes one program instruction per cycle.

# 2.1 CMOS

Complementary metal oxide semiconductor (CMOS) technology was developed in the 1960s. The basic components are MOSFETs (MOS field effect transistor). The term "complementary" in CMOS refers to the use of complementary pairs of Ntype and P-type MOSFETs to construct the logical gates (AND, OR, NOR, etc.), see Figure 1. An N-type transistor lets current pass between the source and drain when the voltage of the gate electrode is positive. A P-type transistor lets current pass when the gate voltage is negative. When one of the paired transistors is on, the other is off, and therefore there is an electric current and power consumption only during the short time the gates are changing state. This is the main advantage of CMOS over the other technologies for building integrated circuits from semiconductors. In other technologies, in one of the states there is a constant current through the transistor.

Figure 1. P- and N-type transistors on a P-substrate.

# 2.2 Chip architecture

The basic parts of an FPGA chip are input/output connections located on the outer edges of the chip, logic blocks, and the connections (wiring routed by switchboxes) between them, as shown in Figure 2. In addition to these, more advanced chips can also have, for example, separate memory, dedicated computation and signal processing blocks, or even a microprocessor. For example, the chip used in [Lu et al., 2010] has a wide range of auxiliary functions.

The main parts of configurable logic blocks (CLB), also known as logic array blocks (LAB), are typically lookup tables and flip-flops [NI, 2008]. These are built from the elementary gates and provide a higher abstraction level for programming the device. Different architectures can have a different number of lookup tables and flip-flops per CLB. Flip-flops, or shift registers, provide one bit of memory each and the lookup tables can describe combinatorial logic. Hence, together they enable the construction of sequential logic with memory. Currently, four or six input lookup tables are typically used.

The wiring runs between the logic blocks and is controlled by switchboxes. The switchboxes connect the logic blocks to the wires and the wires to each other. There is a limited quantity of wiring resources and the design, placement, and distribution of the logic onto the logic blocks must take this into account.

Figure 2. A regular grid FPGA layout.

# 2.3 Antifuse, SRAM, and flash technologies

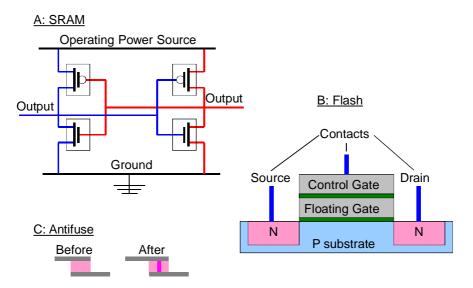

The implementation of FPGA technology comes in three "flavours": antifuse, SRAM (static random access memory), and flash. From a user perspective, the major difference is in how the chip is programmed, that is, how the logic is stored on the chip and how the chip retains its programming. The name refers to the technology used for implementing the switches that control the configuration and connections of wires, and thereby the programming. In all cases, the logic gates themselves are implemented using the same CMOS technology.

A SRAM chip holds the logic in memory only while the chip is powered, that is, it is *volatile* memory, and the chip must be programmed as a part of the start-up sequence. The technology is the same as for the working memory of computers. A chip based on flash technology is reprogrammable like SRAM but it retains the programming without power. Flash technology is essentially the same as in USB memory sticks. The third technology is antifuse, which is not reprogrammable and maintains its programming without power.

SRAM technology holds the programming as the state of groups of crosscoupled transistors. See Figure 3A. Each group forms a bit of memory and determines if a switch is open or closed. While the supply power is provided, the transistors reinforce each other to hold the system in a state of "1" or "0". If the operating power is lost, the state of the transistor system is lost. SRAM consists only of CMOS technology and tends to be at the forefront of development and used in devices which have the highest performance capacity.

The term antifuse comes from fuse, which is a device designed to cut power when the voltage or current through it increases too much. Antifuse functions in the opposite way. It starts out with high resistance and does not let current pass. After it is triggered by, for example, the application of high voltage and current through it, it changes so that its resistance drops and it lets current pass. See Figure 3C. The change is mechanical and irreversible, hence the non-reprogrammability. An antifuse can be implemented by placing a thin layer of non-conducting amorphous silicon between two metal conductors. With the application of sufficient voltage to drive a current through the insulation, the silicon turns into a conducting poly-crystalline silicon-metal alloy.

Flash technology is a variant of EEPROM (electrically erasable programmable read-only memory). The term flash comes from the erasure process of large blocks of data. The method of storing data is based on transistors with a "floating gate", which controls the behaviour of the transistor. See Figure 3B. The floating gate is fully insulated and therefore holds a charge without a power supply. Writing and erasing are performed using a high voltage, which causes the charge in the floating gate to change through hot-electron injection and quantum tunnelling. Flash memory withstands only a limited number of program/erase (P/E) cycles, ranging from a typical value of 100 000 up to a million.

For the design of logical functions, the choice between these technologies has little effect. The differences come into play when physical characteristics, such as

tolerance to operating environment, or operational practices related to, for example, maintenance and data security, are considered. The resources needed for the switches are shown in Figure 4. SRAM requires several transistors, flash requires only one transistor, and antifuse is the smallest and simplest.

Figure 3. Different technologies for storing FPGA configuration data.

# 2.4 Circuit board and connections

The FPGA device is attached to a circuit board, which provides contacts for data signals and operating power. Connections include those to the process instrumen-

tation, measurement data, set point values, and the internal state of the chip. Connections are also needed for programming the device and the other functions on the chip, such as signal processing. There is often separate hardware on the board for, for example, signal processing to perform analog to digital (and vice versa) conversion.

A basic chip based on antifuse technology has no reprogrammable memory, and therefore a separate memory device is required for changing data such as set point values. On the other hand, SRAM devices require separate memory from which to load the configuration at start-up.

# 2.5 Electrical and mechanical properties and reliability

### 2.5.1 Faults

The faults of an integrated circuit can be grouped into permanent faults and transient faults, which can cause incorrect operation, degradation in performance, or complete malfunction. Temporary transient errors are referred to as *glitches*. Gradual aging and degradation can cause the device to malfunction as a sudden event or can lead to a gradual change in performance, as in response time. Manufacturing faults can lead to devices with inferior performance or faster deterioration, or to an entirely non-functional device. Design faults are considered in Chapter 3. Aging, manufacturing, and design faults are all permanent faults. Single event effects (SEE) can be caused by power fluctuation or radiation. A SEE can cause a permanent physical change in the chip, a change in the programming or memory that can be repaired by a restart or "scrubbing", or an incorrect operating state which resolves in normal operation. In [Ziener, 2010], faults are listed and categorised with their error effects. In addition to the integrated circuit, the system includes the circuit board and other electronic components, which are susceptible to additional faults, such as whisker growth on soldered contacts.

#### 2.5.2 Environmental tolerance

As in other electrical and electronic equipment, there are limits to the amount of physical abuse that FPGA-based systems can sustain and still function properly. The damage can be caused by several different kinds of phenomena in the operating environment. Sufficient stress will always cause the equipment to malfunction. Thus, the normal and extreme conditions of the intended operating environment must be taken into account. The section "3.3.1 Environmental Qualification of System" in the licence amendment of the Wolf Creek Generating Station [NRC, 2009b] serves as an example. It covers the topics and how they were tested for that particular application.

Humidity and temperature are tested together and extreme conditions as well as rapid changes in conditions are considered. Humidity refers to non-condensed

air humidity and affects exposed components. Temperature can change the electric properties of materials, alter dimensions of components, and cause damage through thermal shock from rapid temperature change. **Seismic** effects cover acceleration and vibrations from outside forces. Effects of **radiation** are considered in more detail later.

**Electromagnetic compatibility** (EMC) is the equipment's ability to operate in the intended electromagnetic environment without causing or suffering ill effects to or from other electrical equipment. EMC **susceptibility** considers the effects of external sources of electromagnetic fields, that is, other equipment, on the device in question. EMC **emission** considers the effect the device in question has on other equipment. **Surge** and **electrostatic discharge** are abnormally high voltages affecting the equipment. They can enter through the power or signal lines or as discharges of static electricity on contact with the equipment. In NPPs, there is particular interest in the influence between equipment of different safety categories. There is special concern about the influence of lower safety category equipment on higher safety category equipment.

#### 2.5.3 Aging

There are four main aging processes that wear down IC devices. See, for example, [Bernstein et al., 2006, Stott et al., 2010a and 2010b] and the references therein. In [Bernstein et al., 2006], some of the involved physics is explained. The effects can be a gradual deterioration of performance leading to, for example, timing faults, or a sudden event, such as a short circuit.

**Electromigration** (EM) is a diffusive process resulting from the flow of electrons in conductors during operation. The momentum of electrons is transferred to the atoms of the conductor and gradually moves them. Positively charged metal ions are pulled towards the cathode by the electrostatic force, while electrons scattering from the ions push them towards the anode. With high enough current density, the force caused by scattering becomes dominant. The larger the current densities are, the faster the atoms move. In time, this leads to a depletion of atoms on the cathode side and a build-up on the anode side. The conductivity will change and eventually the result is a short or open circuit.

Hot carrier injection (HCI) causes charges to form in the insulating oxide layer of the gate. When a current flows in the channel between source and drain, carriers (negative electrons or positive holes) can be injected and trapped in the oxide layer. The term "hot" refers to the energy of the carriers. The gradually accumulating electric field of the charge in the oxide combines with that of the gate and affects the threshold voltage of the transistor. This leads to slower switching speeds, which causes timing faults.

**Negative bias temperature instability** (NBTI) is caused by trapped charges in the interface of silicon and oxide. This is similar to HCI, but the trapped charges are only positive holes in P-type transistors. The phenomenon is prevalent in high temperatures. The result is a change in the threshold voltage and timing performance.

**Time-dependent dielectric breakdown** (TDDB) results from the electric field applied across the insulating oxide layer (the dielectric). TDDB is also known as oxide breakdown. The process starts with charges being trapped in the oxide. The material gradually deteriorates, the potential barrier it creates decreases, and conductive paths begin to form. Higher temperatures and stronger electric fields accelerate the process. The result is first an increase in leakage current and eventually a short circuit.

#### 2.5.4 Whisker growth

Whisker growth [NASA/Tin whiskers, Fang et al., 2006] is a phenomenon in which filaments of metal build up and protrude from the surface. It is a slow gradual process of crystal formation due to a number of possible causes. The whiskers are thin but can grow to several millimetres. This is not a chip-level issue but affects the board and soldered connections mostly. A major concern is the potential for short circuits that the whiskers can cause. The problem has become a more relevant issue after certain materials (in particular lead) have been banned in electronics for environmental reasons. Whisker growth is more common in pure tin solder than tin-lead alloy solder.

#### 2.5.5 Radiation dose and single event effects

Radiation effects on ICs have been mostly studied in relation to aviation and space flight. The radiation at high altitudes and in space is much stronger than at sea level under the protection of the atmosphere. See, for example, [Quinn, Graham, 2005]. Radiation can cause both gradually developing effects and sudden changes. The gradual changes are due to the total ionizing dose accumulating over time and are rather similar to the aging processes. The sudden effects, or single event effects, are caused by a hit from a single energetic particle.

The effect of the total ionizing dose (TID) is due to high energy radiation causing the formation of electron-hole pairs in the transistor's dielectric. This causes a build-up of charge that interferes with the control voltage of the gate. The threshold voltage changes, there will be an increase in leakage current, and the timing properties change. Eventually there will be a functional failure. Either the performance deteriorates so much that correct functioning is no longer achieved, or a there is a sudden failure as a result of, for example, dielectric breakdown and a short circuit.

Whereas TID takes time to develop, single event effects (SEE) caused by a single energetic particle are instant randomly occurring effects that include single event upset (SEU), single event transient (SET), single event latchup (SEL), single event gate rupture (SEGR), single event burn-out (SEB), and single event snap back (SES) [Wang, 2003, Sexton, 2003].

A single event upset is a soft error in the memory of the device. A soft error is one that does not cause permanent physical damage to the device. The energy transferred by the radiation, an ionizing particle, can cause the state to change in a memory element. If sufficient charge is transferred to disturb the voltages of the transistors in a SRAM element, the state of memory may not recover to the correct value but may settle to the incorrect value. Alternatively, a voltage pulse caused by the particle can propagate through the circuit and alter the value of a memory element if the pulse arrives at a memory element at a suitable moment. The term single event functional interrupt (SEFI) is used if the upset affects the program memory and alters the functional configuration.

A single event transient is a voltage pulse propagating through the circuit. It can cause timing errors by shifting or introducing additional clock edges when the pulse is on a clock line. Incorrect value and operation can result if the pulse is on a data line. If the outcome is not transient, that is, if the pulse causes a change in memory, the effect is considered to be a SEU.

A single event latchup is a latchup with this specific initiating cause. Below is a more general discussion of a latchup. A single event snap back is similar to a latchup but the parasitic pnpn structure is not required. Both cause a high current that can destroy the transistor.

A single event gate rupture occurs when an energetic particle (a heavy ion) creates plasma of electron-hole pairs while there is a voltage applied across the dielectric. Somewhat different models of the chain of events leading to failure of the gate oxide are given in [Schwank et al., 2008] and [Sexton, 2003].

Single event burnout [Sexton, 2003] is an event observed in power bipolar (both holes and electrons act as carriers) transistors and MOSFETs, which control high voltages. A heavy ion hit triggers a condition known as second breakdown (a combination of excess voltage and current), in which the increased current heats up and destroys the transistor.

The different technologies, antifuse, flash, and SRAM, are compared in [Wang, 2003] and [iROC, 2004]. Antifuse is the most resistant to effects of radiation, while SRAM is the most susceptible. All three have the same CMOS technology for the gates but SRAM also has CMOS for the switches controlling the wiring and configuration.

The devices can be designed to be more resistant to radiation, or *radiation hardened*, through manufacturing techniques. The use of different materials and manufacturing techniques is considered in [Schwank et al., 2008]. The hardening is a part device fabrication, and thus using a COTS (commercial off the shelf) device limits the available selection. A specially designed and manufactured hardened version of a device would be significantly more expensive.

#### 2.5.6 Current leakage

In theory, CMOS components use energy only when the states change. However, insulation is not perfect and while there is a voltage difference, there will be a small current. This unintentional current is referred to as leakage current. A small current passes through the transistors and also through the oxide of the gate. The

smaller the components and the thinner the insulation, the greater the current leakage will be. This additional energy consumption leads to increased heating, which in turn leads to other effects. For example, aging effects and timing are affected by temperature. Since the leakage happens in every transistor, even if the transistor is not actually used for implementing the logic, FPGAs with large numbers of transistors need to take it into account.

### 2.5.7 Latchup

CMOS technology uses paired NMOS (npn structure of N- and P-type semiconductors) and PMOS (pnp structure) transistors. Their proximity creates an unintentional parasitic pnpn structure which can enter a low impedance and high current state known as latchup [Morris, 2003]. When in latchup, the pnpn structure is a short circuit and current continues to flow through both transistors as long as the operating voltage is available. The heat generated by the current can destroy the device. Smaller scale and smaller components increase latchup risk while decreasing operating voltage reduces it.

Latchup requires an initiating event, which can be operating power fluctuation, radiation induced voltage pulse, or circuit switching noise. A trigger current in the transistors needs to be exceeded to initiate a latchup. To maintain it, the operating voltage must exceed holding voltage. If the holding voltage is not exceeded, a soft latchup can still occur. In a soft latchup, the initiating event triggers a latchup, which then recovers but the data or state of memory may be corrupted.

In silicon on insulator (SOI) technology the transistors are built on an insulating layer. Because there is no conductive path between the transistors, a parasitic pnpn structure is not formed and latchup cannot occur. This technology is becoming more common in space systems [Schwank et al., 2008].

#### 2.5.8 Manufacturing technology size scale

Earlier it was mentioned that the manufacturing techniques and choice of materials can affect the radiation tolerance, or *hardness*, of the device. One issue to consider when choosing a device is the size scale of the technology. As the manufacturing technology of ICs has progressed, a major direction has been the decrease in size of the components and width of wiring on the chip. Currently technologies smaller than 100 nm are used. The "XX nm" technology is a naming convention, not an exact size of the components on the chip. Originally it referred to the size of the gate, that is, the distance between the source and drain. As the size decreases, the component's robustness decreases. Radiation susceptibility increases, aging processes may hamper the operation sooner, and heating issues may become problems. Using an older more robust technology is therefore advisable if the capacity of the device is sufficient.

# 2.6 Timing, clock skew, and race condition

The flip-flops of a circuit are clocked to change value at specific times according to a clock signal, that is, at the rising or falling edge of a square wave clock signal. For the component to function properly, the input signal should remain steady for *set-up time* before the clock edge and *hold time* after the clock edge. The components do not react instantly but there is a small delay from the clock signal arriving to the output changing. If the input signal changes value, or is still in the process of changing too close to the clock edge, a timing error, such as an incorrect or metastable state, may result. The shorter the clock period, that is, the higher the operating frequency, the faster the components need to be to operate correctly.

Clock skew is the phenomenon of the clock signal arriving to components at different times. The cause is due to finite signal propagation speed and routing of the signals. The clock skew between components under ideal conditions can be determined from the layout and properties of the components and the wiring between them. However, the amount of clock skew is affected by factors such as temperature and the effects of aging on the circuit.

*Timing margin* is the increase in clock period from the minimum value necessary for correct operation. Its purpose is to avoid timing faults due to the variation in component properties and clock skew.

The term *race condition* refers to a situation in which the output of computation depends on the timing between signals, that is, the result is determined by the order in which the "racing" signals arrive. Poor timing can cause a gate to change state more than once during a cycle, which in turn can lead to, for example, meta-stability or the incorrect state propagating further.

# 2.7 Metastability

Metastability is a state in which the logical state is not properly defined. The circuit does not settle to either "1" or "0" but remains in between or oscillates between the values. It is caused by a timing error and persists for an indefinite time [Altera, 2009, Erickson, 2000].

Short-lived metastable states are more common than those of a long duration. The mean time between failures increases at an exponential rate to the recovery time. The recovery time should be taken into account when determining the clock frequency of the circuit. Even though the situation resolves itself, the error may have propagated and corrupted the state of the system. If the clock frequency is slower, there is more time for the metastability to resolve between clock cycles so that the value is correct by the time the next component reads it.

To avoid metastability, the timing of the circuit should be carefully analysed for worst case performance. External input signals to the circuit and signals from components that change value slowly should be synchronised. Flip-flops in sequence form a synchroniser and each reduces the probability of a metastable state propagating further. The system may end up in an inconsistent state if two or more components use the metastable value and interpret it differently. This can lead to difficult to identify byzantine faults [Driscoll et al., 2003].

# 2.8 Parallel computing

One distinct difference between microprocessor-based systems running software and those using pure hardware such as ASIC or FPGA lies in parallel processing of the "program". A microprocessor executes a single instruction of a single program per clock cycle. Of course, more than one processor can execute multiple programs which interact, but this complicates matters even more. An FPGA application executes all "instructions" on each clock cycle. Furthermore, there is separate hardware for each "instruction" of every program.

In parallel processing, different functions (for software this includes the operating system, driver software, and other functions of the platform) do not compete for the same processor time or memory resources. Timing, from the perspective of all instructions to be finished in time, is more reliable, but the order the instruction are executed is subject to the timing properties of the circuit. Different applications can be placed on different FPGA devices on different circuit boards to prevent harmful interaction and platform-related random-event common-cause failures.

# 2.9 System on a chip – SOC

The newer FPGA devices hold much more than just the configurable logic blocks. On the same chip, there can be a number of dedicated computational cores including complete microprocessors. In addition to the memory provided by the registers (flip-flops) in the logic blocks, separate blocks of memory are available. Signal processing units for analog-to-digital and digital-to-analog conversion are available along with more advanced hardware for communications. Actel's flashtechnology-based SmartFusion chip is an example of an advanced chip proposed for an NPP application [Lu et al., 2010].

As less and less hardware is needed on the circuit board in addition to the FPGA device itself, the designs are moving towards SOC solutions which are effectively complete computers on a single silicon chip.

# 2.10 FPAA – a glimpse of analog technology

Field Programmable *Analog* Array (FPAA) is in a way the counterpart of FPGA in analog technology. The philosophy is quite similar but instead of logic blocks, a FPAA chip contains configurable analog blocks (CAB). FPAA technology is younger than FPGA and is still in its infancy. See, for example, [Hall, 2004]

# 3. Application design and development

Even though the final product is a hardware component, the design and implementation of an FPGA-based system has strong similarities with software-based systems. A number of hardware description languages (HDL) or higher-level languages rather similar to software programming languages are typically used. This, together with the automated design tools, makes it very easy to define very complex functions. The steps of design use software tools to transform the design from one representation to another. The final output of the design process before configuring an actual device is a binary configuration code. FPGA device vendors have their own IDE (integrated development environment) tools that typically support at least the different design steps and simulation testing.

A characteristic of systems implementing complex functions or using a complex framework or platform, such as software and other programmable I&C, is the presence of errors of a deterministic nature (in addition to randomly occurring faults). The system does not fail randomly, but for a specific input the output is always incorrect.

Despite the similarities with software design, aspects of hardware design must be understood by the designer. The levels of abstraction that a software-based system offers are not present in FPGA design. There is no system level or an operating system behind which the hardware issues are hidden. On the other hand, the complexity caused by the shared computing environment and interaction with other programs is absent.

With both hardware and software aspects present, FPGA design and implementation can be characterised as "hardware implementation designed like software." It is quite commonly agreed in the literature that, for applications with strict reliability and safety requirements, a design life cycle similar to software should be used.

In the following, we first describe a generic simplified design flow for an FPGA application. The each step and related issues are discussed in more detail. Finally, a number of design issues of particular interest are considered in more depth. The perspective of evaluating and reviewing an FPGA-based system, along with extensive lists of issues to consider, is given in [NRC, 2010b].

The following presentation focuses mainly on the design of the FPGA's functions and the logic it implements. The connection of the chip onto the circuit board along with the board's properties and connections are mostly ignored. Whereas functions are designed for a particular application, the FPGA device, circuit board, and related equipment are likely to be generic hardware combinations or platforms with few ties to a particular application field or industry.

A detailed beginner-level introduction to generic FPGA application development is given in [Smith, 2010]. More specific focus for nuclear power is provided in [Fink et al., 2010, Bobrek et al., 2009, Alvarado, Herrell, 2009].

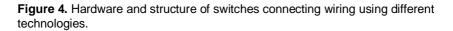

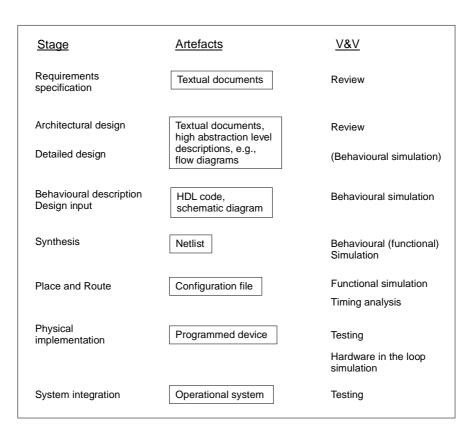

# 3.1 Design life cycle, stages, and work flow

The first step is requirements specification. The requirements cover both logical functions and the physical hardware-related properties. Typically the requirements are drawn from the purpose of the system and the environment in which it is to operate. The result of requirements specification is usually a textual document with a list of requirements.

Based on the requirements, the chip type is selected, architectural design and detailed design of the application are performed. Architectural design considers the functions more as modules of abstract functions, while detailed design considers the specifics of implementation.

Code generation, or another form of inputting the design, implements the functions in a way similar to software code. The code must then be synthesised into a lower abstraction-level description of the functions and mapped onto the device hardware.

Verification and validation (V&V) is performed alongside the design. This includes various reviews, simulations, and tests. Reviews are used mainly in the earlier stages of design flow, where a higher level of abstraction is used for the descriptions, and simulations are used in the later stages. Static analyses can also be performed to, for example, analyse the code structure and style, timing performance, and correctness of the implemented logic.

The design process is iterative as it is likely that, at some point, a previous step will need to be revised or redone. For example, verification of the design step may fail or it may be discovered that some additional functions are needed or requirements need to be satisfied for correct and safe operation.

The naming of the design stages or phases is not universal and varies slightly in the literature. Some stages may be missing entirely or the definition may be different. See, for example, [Gaisler Research, 2002, NRC, 2010b]. The design stages and life cycle are depicted in Figures 5 and 6.

Figure 5. FPGA application design stages and related output (artefacts) and verification actions.

Figure 6. V-model of design life cycle.

# 3.2 Requirements specification

The purpose of requirements is to provide an objective and guidelines for the design process by specifying the properties of the final product. The requirements are based on the upper levels of system design and the role of the component or system to be designed. The core of the requirements is the specification of the functions of the device. The description includes the context and the environment in which the device operates. This means both the physical environment, for example, the temperature and radiation conditions, and the technological and "logical" environment, being the other systems it interacts with. In addition to the normal operating conditions, various extraordinary conditions need to be taken into account, such as the response to incorrect inputs, internal faults and fault tolerance, and changes in physical conditions.

The software aspects of the requirements mostly focus on the functional behaviour of the device, such as the purpose of operation and the reaction to certain inputs, but also things such as self monitoring, testability, and fault recovery. Requirements on hardware aspects may specify such things as connections and board size, response time and clock cycle, and mechanical acceleration (vibration) tolerance.

Requirements specification is one of the stages that often needs to be amended during later stages of design. Prior to knowing details of the design in question, and also the devices it interacts with, it is difficult to discern all the situations and conditions that may arise during operation and need to be prepared for.

# 3.2.1 ESL – electronic system level

An emerging trend is that an entire electronic system is described using a unified approach on a functional level, including all hardware, software, communications, and the functions they implement. This high-level description is usually created using a high abstraction level language, such as System C (essentially C++), System Verilog, or Matlab [Gassino, 2009]. Each part of the whole is represented by a component model that interacts with the other components. The behavioural models along with the communications form the overall system. This allows functional simulation of the system before any of the components are designed. The designers can test different allocations of functions and resources to components to find the best configuration. This electronic system level (ESL) description can then be used to derive requirements for the components. It may even be possible to generate the HDL code directly from the ESL description.

# 3.3 V&V: requirements

The output of the requirements specification consists typically of text documents with only a loose structure that is not suitable for automatic structured analysis and

verification. On the other hand, specifications drawn from an ESL description may even enable some level of behavioural simulation. For the most part, the verification is a series of inspections and reviews of the documents. The reviews should be performed by independent experts with no ties to the design team but sufficient skill and knowledge of the application area and design process. In particular, verifying that all necessary requirements are present may be difficult and requires indepth understanding and expertise. Some structured review techniques are considered in [Lahtinen, 2012].

Traceability of the requirements is an issue of particular concern that spans the entire life cycle. The fulfilment of the requirements should be traceable through design stages to the final product. Throughout the design process, it should be possible to trace choices and decisions back to the requirements. In addition to all the requirements to be fulfilled, there should not be any requirements added in later stages but not included in the actual requirements specification. Hence, work practices and tools should be chosen to support traceability.

# 3.4 Architectural design

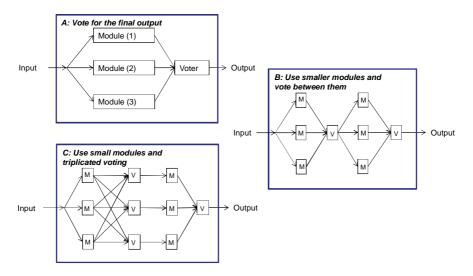

In architectural design, also referred to as high-level design, the functions are divided into smaller modules (blocks) and their interactions are specified. Several reliability considerations are relevant during architectural design. The design affects the possibilities to use, for example, redundancy and error correction, and also affects the overall robustness of the design. The use of TMR (triple modular redundancy) on the higher levels needs to be designed at this stage. Due to the limited number of input/output pins on the device, the internal state of the chip is not fully detectable during testing or operation and the choice of modularity affects the available data. In addition, the possibility to control the execution of specific functions depends on the division.

While designing the modularity, the use of pre-developed components and repeating structures should be considered. Some of the functions can be implemented using modules developed by third parties, or IP (intellectual property) cores. One approach that aims for designs of high reliability is to split the design into small simple functions that can be verified and use them as the basis for more complex functions [Kojima et al., 2010, Lach et al., 2005 and 2006].

# 3.5 Detailed design

Detailed design specifies the particulars of implementing the functions of the modules. Decisions are made about, for example, the use of memory, state machines, and redundancies. This stage does not necessarily exist as a separate stage in the design process, but it can be included in the earlier design stage and the following behavioural description. Whereas the architectural design is for the most part independent of the hardware aspects, detailed design is more involved with the resources available on the device, timing properties, and the clock cycle to be used.

# 3.6 V&V: architectural and detailed design

Depending on the tools and format, different verification methods may be available. While the functions are not specified in detail, inspection and review are still likely to be the main methods.

# 3.7 Behavioural description and design entry

The design is implemented as hardware description language (HDL) code, a schematic diagram, or another description of the functions. (The word *implementa-tion* can refer to a number of different things and stages of the design process.) This stage corresponds to writing program code for a software-based application. The most common method today is the use of a HDL; in particular, VHDL or Verilog languages are used.

The use of high-level languages can lead to complex and intractable descriptions which in turn hinder V&V activities. Therefore, strict rules should be applied to the use of the languages. Only clear and easily understandable structures should be used and the allowed features of the language should be restricted to a suitable subset of the language. The approach is the same as using a subset of a programming language, such as MISRA C (Motor Industry Software Reliability Association), in software-based systems. The ESA (European Space Agency) has specified guidelines for the use of VHDL [ESA, 1994].

# 3.7.1 Hardware description languages – HDL

Hardware description languages (HDL) are rather similar to software programming languages. They are used to describe the functions, not the physical components or connections. The abstraction level is on the RTL (register transfer level) and has little to do with the circuitry that eventually implements the functions. Like programming languages, HDLs use variables, parameters, and subroutines. However, the execution of the codes is different because software is executed one instruction at a time, possibly on two or more parallel threads, whereas the implementation of HDL code "executes" in a fully parallel environment with separate hardware for each "instruction". Consequently there are differences in, for example, the operators of the languages. Code examples of VHDL and Verilog, along with recommendations for good coding style and practices, can be found in [NRC, 2010b].

The most important HDLs are VHDL [IEEE 1076-2008] and Verilog [IEEE 1364-2005]. Both are standards but neither is a formal language that would allow strict

analysis and verification of the code and functions. VHDL (very high speed integrated circuit HDL) is built on the ADA programming language and has much in common in structure and syntax. Verilog, on the other hand, was designed to have a syntax similar to C.

In [Gassino, 2009], a relation is drawn between HDLs and software programming languages. Despite the differences in parallel or sequential execution, the two implementations are more or less interchangeable. As a part of the development process, the HDL descriptions are simulated on computers, thus showing that software can do the same task as hardware implementation. On the other hand, software runs on a microprocessor, which is hardware, and can be implemented using a programmable device.

#### 3.7.2 Higher-level entry methods

In addition to HDLs, more complex entry formats can be used in design. These include C, Matlab, and LabView. One approach available in the Xilinx Embedded Development Kit is to provide C code that is then executed on a soft processor core generated by the development kit. Other tools convert C or Matlab code into HDL code [Huffmire et al., 2008, MathWorks].

When the design is generated in a higher abstraction level language, creating and managing complex structures is simpler from the perspective of the designer. This speeds up the design process and should result in fewer errors in the design on the part of the designer. One disadvantage is the temptation to create more and unnecessarily complex designs. Another disadvantage is the need for one more tool and one more conversion between the designer's original intent and the final product, as more of the details of the design are left for the tools to decide. Additionally, the generated HDL code can be very difficult to read.

SystemVerilog aims for a higher level description of the system and hardware with verification in mind: "Hardware Description and Verification Language" (HDVL) [System Verilog]. Verilog and SystemVerilog have been merged in [IEC/IEEE 62530-2011]. SystemC is based on C++ and provides a set of classes for description and simulation of hardware at the system level [OSCI, IEEE 1666-2005].

Esterel is a programming language that allows generation of VHDL and Verilog code for hardware, in addition to C code for software [Boussinot, de Simone, 1991, Brandt, Schneider, 2008]. It is designed to support formal specification and verification. An IEEE standards development working group is developing Esterel v7 Language Reference (IEEE P1778).

#### 3.7.3 Other entry methods

Hardware description languages are already rather high abstraction level descriptions. Simple logic can be designed using gate-level descriptions. Graphic EDA (electronic design automation) tools are available for entering the design using schematic or block diagrams. Schematic diagrams are lower abstraction level descriptions of components, such as gates and lookup tables, while block diagrams use a higher level abstraction of functions.

# 3.8 Intellectual property – IP cores

The manufacturers of FPGA devices, as well as independent providers, offer predeveloped modules to be used as part of a design. This is similar to pre-developed software or library routines in software-based systems. The IP cores can be small routines implementing simple logic or larger entities for both frequently used functions and specialised tasks.

Delivery format and design level of the IP cores can vary. They can come as high-level description HDL code, netlists that are not device specific, or device-specific binary files. Factors affecting the format include issues such as IP security, from the developer's point of view, and the format is not always the best choice from the user's perspective. IP cores distributed as RTL level descriptions, such as HDL code, or as netlists are referred to as soft cores. IP cores distributed as device-specific (partial) configuration files are referred to as hard cores.

For safety-related applications with high reliability demands, the use of IP cores should be restricted to well-tested products from reliable sources. In [NRC, 2010b], it is recommended that in safety-critical systems, IP cores are avoided or additional verification of the core is performed. In addition to safety and reliability, there are security considerations related to the use of IP cores. Aspects of IP core security issues are considered in [Ziener, 2010].

Applications are typically developed using system platforms that include, in addition to development tools and hardware infrastructure, a set of predeveloped functions that serve as building blocks. Unlike third party IP cores, these are likely to be developed under strict requirements, if they are a part of a platform intended for NPP applications. Plans to use third-party certified SIL3 block libraries are underway.

# 3.9 V&V: design entry

In addition to inspection and review of the design, or diagrams and code, the format of the design allows simulation. Behavioural simulation is an important verification method at this stage. Details of the hardware are not available and therefore proper functional simulation is not yet possible. The test vectors, or the inputs and expected outputs, need to be designed carefully to cover the specifications and both normal and exceptional operating conditions. Additionally, faults and errors should be included in the tests, for example by use of fault injection methods. This allows wider test coverage than just the manipulation of input values. It also enables the testing of the effects of SEEs and other hardware failures and the correct behaviour of fault detection and recovery functions.

Both intermediate results (internal states of the design and inputs/outputs of functional blocks) and final outputs should be verified. Separate simulations can