# TIEDOTTEI

# Timo Malm & Maarit Kivipuro

# Safety validation of complex components Validation by analysis

| V | Т | Т | Т | i | е | d | 0 | t | t | е | i | t | а |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| V | Т | Т | Т | i | е | d | 0 | t | t | е | i | t | а |

|   | Т | Т | Т |   |   |   |   | t | t |   |   | t |   |

| V | Т | Т | Т | i | е | d | 0 | t | t | е | i | t | а |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| V | Т | Т | Т | i | е | d | 0 | t | t | е | i | t | а |

| V | Т | Т | Т |   |   |   |   | t | t |   |   | t |   |

TECHNICAL RESEARCH CENTRE OF FINLAND

# Safety validation of complex components Validation by analysis

Timo Malm & Maarit Kivipuro VTT Automation

European Project STSARCES Contract SMT 4CT97-2191

TECHNICAL RESEARCH CENTRE OF FINLAND ESPOO 2000 ISBN 951-38-5657-7 (soft back ed.) ISSN 1235-0605 (soft back ed.)

ISBN 951–38–5658–5 (URL: http://www.inf.vtt.fi/pdf/) ISSN 1455–0865 (URL: http://www.inf.vtt.fi/pdf/)

Copyright © Valtion teknillinen tutkimuskeskus (VTT) 2000

### JULKAISIJA – UTGIVARE – PUBLISHER

Valtion teknillinen tutkimuskeskus (VTT), Vuorimiehentie 5, PL 2000, 02044 VTT puh. vaihde (09) 4561, faksi (09) 456 4374

Statens tekniska forskningscentral (VTT), Bergsmansvägen 5, PB 2000, 02044 VTT tel. växel (09) 4561, fax (09) 456 4374

Technical Research Centre of Finland (VTT), Vuorimiehentie 5, P.O.Box 2000, FIN–02044 VTT, Finland phone internat. + 358 9 4561, fax + 358 9 456 4374

VTT Automaatio, Turvallisuustekniikka, Hermiankatu 8 G, PL 1307, 33101 TAMPERE puh. vaihde (03) 316 3111, faksi (03) 316 3495

VTT Automation, Säkerhetsteknik, Hermiankatu 8 G, PB 1307, 33101 TAMMERFORS tel. växel (03) 316 3111, fax (03) 316 3495

VTT Automation, Safety Engineering, Hermiankatu 8 G, P.O.Box 1307, FIN–33101 TAMPERE, Finland phone internat. + 358 3 316 3111, fax + 358 3 316 3495

Technical editing Maini Manninen

Malm, Timo & Kivipuro, Maarit. Safety validation of complex components – Validation by analysis. Espoo 2000. Technical Research Centre of Finland, VTT Tiedotteita – Meddelanden – Research Notes 2022. 46 p. + app. 4 p.

Keywords safety validation, complex components, failure mode, effect analysis, FMEA

# Abstract

The aim of the safety validation process is to prove that the product meets the safety requirements. Safety validation of complex programmable systems has become an increasingly common procedure since programmable systems have turned out to be useful also in safety related systems. However, a new kind of thinking related to the whole life cycle of the programmable product is needed and new validation methods (analysis and testing) to support the old methods are inevitable. This means that methods such as failure mode and effect analysis (FMEA) are still applicable, but they are not sufficient. Methods are needed also to guarantee the quality of the hardware and software.

The main validation methods are analysis and tests, and usually both are needed to complete the validation process. Analysis is very effective tool to validate simple systems thoroughly, but a complete analysis can be ineffective against failures of modern programmable electronics. Large programmable systems can be so complicated that a certain strategy in the validation process is necessary to keep the resources required reasonable. A good strategy is to start as early as possible and at the top level (system level). It is then possible to determine the safety critical parts by considering the safety requirements, categories (according to EN 954) [EN 954-1 1996], safety integrity levels (according to IEC 61508) [IEC 61508-1 1998], and the structure of the system. The critical parts are typically parts that the system rely on and which have some properties which cannot be seen clearly at the top level.

A newly arising problem is that large programmable systems are becoming difficult to realise and the analysis is often difficult to understand. Figures can often illustrate the results of the analysis better than huge tables. However, there is no all-purpose excellent illustrating method, but the analyser needs to draw figures so that the main subject is well brought out.

# Preface

STSARCES, the Standards for Safety Related Complex Electronic Systems project, is funded mainly by the European Commission SMT (Standards, Measurement and Testing) programme (Contract SMT 4CT97-2191). Work package 3.1 is also funded by the Finnish Work Environment Fund, Nordtest, and VTT. The project aim is to support the production of standards for the functional safety sector of control systems in machinery. Some standards are already available and industry and research institutes have their first experiences in how to apply the standards. Harmonisation of methods and some additional guidelines to show how to apply the standards are needed since the methods for treating and validating safety related complex systems are complicated and not particularly detailed. This report introduces the results of work package 3.1: Validation by analysis. The final format of the report was achieved with help, discussions and comments from Jarmo Alanen, Risto Kuivanen, Risto Tiusanen, Marita Hietikko, Risto Tuominen and partners from the consortium.

The following organisations participated in the research programme:

- INERIS (Institut National de l'Environnement Industriel et des Risques, of France)

- BIA (Berufsgenossenschaftliches Institut für Arbeitssicherheit, of Germany)

- HSE (Health & Safety Executive, of United Kingdom)

- INRS (Institut National de Recherche et de Sécurite, of France)

- VTT (Technical Research Centre, of Finland)

- CETIM (Centre Technique des Industries Mecaniques, of France)

- INSHT (Instituto Nacional de Seguridad e Higiene en el Trabajo, of Spain)

- JAY (Jay Electronique SA, of France)

- SP (Sveriges Provnings- och Forkningsinstitut, of Sweden)

- TUV (TUV Product Service GMBH, of Germany)

- SICK AG (SICK AG Safety Systems Division, of Germany)

The research programme work-packages were assigned as :

- Work-package 1: Software safety (leader – INRS)

WP 1.1 Software engineering tasks: CASE tools (CETIM)

WP 1.2 Tools for software faults avoidance (INRS)

- Work-package 2: Hardware safety (leader – BIA)

WP 2.1 Quantitative analysis (BIA)

WP 2.2 Methods for fault detection (SP)

- Work-package 3: Safety validation of complex components (leader – VTT)

WP 3.1 Validation by analysis (VTT)

WP 3.2 Intercomparison white-box/black-box tests (INSHT)

WP 3.3 Validation tests (TÜV)

- Work-package 4: Link between the EN 954 and IEC 61508 standards (leader HSE)

- Work-package 5: Innovative technologies and designs (leader INERIS)

Operational partners: Industrial (SICK AG and JAY) and test-houses (INERIS and BIA)

- Work-package 6: Appendix draft to the EN 954 standard (leader – INERIS)

Operational partners: STSARCES Steering Committee and industrial partners

Tampere, 22.2.2000

Authors

# Contents

| Al | BSTR | ACT      |                                                  | 3  |  |  |

|----|------|----------|--------------------------------------------------|----|--|--|

| PF | REFA | СЕ       |                                                  | 4  |  |  |

| GI | LOSS | ARY      |                                                  | 8  |  |  |

| 1  | INT  | RODUC    | TION                                             | 9  |  |  |

| 2  | VAI  | JIDATIO  | ON PROCESS                                       | 11 |  |  |

|    | 2.1  | The Ne   | ed for Validation                                | 11 |  |  |

|    | 2.2  | Safety   | Validation                                       | 12 |  |  |

|    |      | 2.2.1    | Validation Planning                              | 13 |  |  |

|    |      | 2.2.2    | Validation                                       |    |  |  |

| 3  | SAF  | ETY ISS  | SUES RELATED TO COMPLEX COMPONENTS               | 14 |  |  |

|    | 3.1  | Analys   | ing Strategy                                     | 14 |  |  |

|    | 3.2  |          |                                                  |    |  |  |

|    |      | 3.2.1    | Analysing Strategy for Modules and Systems       | 16 |  |  |

|    |      | 3.2.2    | Safety Principles of Distributed Systems         | 17 |  |  |

|    | 3.3  | Comple   | ex Components                                    | 24 |  |  |

|    |      | 3.3.1    | Failure Modes for Complex Components             | 25 |  |  |

|    |      | 3.3.3    | Safety Aspects                                   |    |  |  |

| 4  | MET  | THODS    | OF ANALYSIS                                      | 29 |  |  |

|    | 4.1  | Comm     | on Analysis Methods                              |    |  |  |

|    |      | 4.1.1    | FMEA                                             |    |  |  |

|    |      | 4.1.2    | FTA                                              |    |  |  |

|    | 4.2  | Illustra | ting the Results of a Safety Analysis            |    |  |  |

|    |      | 4.2.1    | The Need to Clearly Show the Results of the FMEA |    |  |  |

|    |      | 4.2.2    | Examples for Illustrating FMEA Results           |    |  |  |

|    |      | 4.2.3    | Conclusions for Methods of Illustration          | 40 |  |  |

| 5  | CON  | CLUSI    | ONS                                              | 43 |  |  |

| RI | EFER | ENCES.   |                                                  | 44 |  |  |

| AI | PPEN | DIX A    |                                                  |    |  |  |

# Glossary

| Bottom-up<br>method/analysis/<br>approach | The analysis begins with single failures (events) and the consequences are concluded.                                       |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| CAN-bus                                   | Control area network; communication method which is common in distributed systems, especially, in mobile machines and cars. |

| Component level<br>analysis               | Analysis is made on level in which the smallest parts are components.                                                       |

| CPU                                       | Central processing unit.                                                                                                    |

| FMEA                                      | Failure mode and effect analysis.                                                                                           |

| FTA                                       | Fault tree analysis.                                                                                                        |

| Module level<br>analysis                  | Analysis is made on level in which the smallest parts are modules (subsystems).                                             |

| SIL                                       | Safety integrity level (IEC 61508).                                                                                         |

| System level<br>analysis                  | Analysis is made on high level in which the smallest parts are subsystems.                                                  |

| Top-down<br>method/analysis/<br>approach  | The analysis begins with top events and the initiating factors are concluded.                                               |

# **1** Introduction

During the 1980's, it was realised that it was not possible to thoroughly validate complex programmable electronic components and this resulted in complex electronic components not being used in safety critical systems. However, complex components make it possible to economically perform new complex functions without using many extra components, therefore the possibility of using complex programmable components to also perform safety functions increased. The methods for validating complex systems have developed significantly and they still continue to develop, and as a result, there are currently methods to validate control systems that include complex components.

Complicated integrated circuits and programmable circuits are considered as complex components, however, small devices like sensors or motor control units can be called complex components when the observer has a system point of view. The component is usually a part, which is not designed by the system designer and is bought as a whole; therefore, it is the smallest part that the system designer is controlling. This study is considering the analysis of complex components from different points of view and, therefore, the concept of complex components has several meanings.

Complex components within safety related systems are becoming increasingly common. One reason for this trend is that in general, systems are getting more and more complex and the monitoring and safety functions required are also complicated, therefore more complex control systems are required. This results in very complex systems, where the structures and the functions are difficult to understand and it can be a major problem for the validators. Desired features in safety systems are certain levels of redundancy and diversity, but they make the systems even more complex and difficult to thoroughly understand.

Since the components and the systems are complex they tend to include design errors because it is very difficult to verify, analyse, and test the complete system. Another problem is that the exact failure modes of complex components can also be difficult to predict. The question is, 'can people trust the complex safety systems?' If a safety function fails it often causes dramatic consequences since people take higher risks when they feel they can trust the safety system, and it is therefore important for safety systems to perform their safety functions reliably. A validation process provides proof that a safety system fulfils its safety requirements. This report gives guidance on one part of the validation process – validation by analysis, and in particular considers, systems including complex components.

Although complex programmable components can be difficult to validate, they make it possible to perform new kinds of safety and monitoring functions, for example, programmable systems can monitor reasonability of inputs and complicated safety limits, whereas normally these functions would be laborious and expensive to perform with hardwired technology. Therefore complex programmable safety related systems are becoming more common in areas where they are economically competitive. The designer has to decide whether he can accept the risks programmable systems bring along whilst also utilising the possibilities they give.

# 2 Validation process

### 2.1 The need for validation

In general, a validation process is made to confirm by examination and provision of objective evidence, that the particular requirements for a specific intended use are fulfilled. When validation is related to the safety-related parts of a control system, the purpose is to determine the level of conformity to their specification within the overall safety requirements specification of the machinery. [prEN 954-2 1999].

Carrying out a validation process can be a laborious task especially for complicated systems, which have got high safety demands. However, although the process can be laborious it is also necessary. Validation is often needed for the following purposes:

- to prove to customers that the product is applicable for the intended purpose,

- to prove to authorities that the product is safe and reliable enough for the intended purpose,

- to prove to the manufacturer that the product is ready for the market,

- to prove the reasons for specific solutions,

- to provide documentation to help with future alterations of the product,

- to prove the quality of the product.

The validation process has been growing to meet the common needs as the technology has developed. Simple systems can be analysed (FMEA) and tested (fault injection) quite thoroughly. Systems with moderate complexity can also be analysed quite thoroughly, but the tests cannot cover the whole system. Very complex systems cannot be completely analysed in detail and thorough tests are also not possible. A number of different methods are needed in the process. Analysis is required in at least the system level and the detailed component level, but also requirements related to different lifecycle phases have to be fulfilled. This means that attributes such as quality control, correct design methods and management become more important since most of the failures or errors are related to these kind of issues.

Confidence is a very important factor related to the validation process. The user of the validation documents has to trust the validation quality, otherwise the validation has no meaning. The validation activities are actually carried out to convince someone that the product is properly designed and manufactured. One way to increase the confidence is to perform the validation process according to existing requirements and guides, and to have objective experts involved in the validation process.

### 2.2 Safety validation

The safety validation process consists of planning and the actual validation. The same process can also be applied for subsystems. A checklist or alternative guide is required in the process to include all the necessary actions for the safety validation plan.

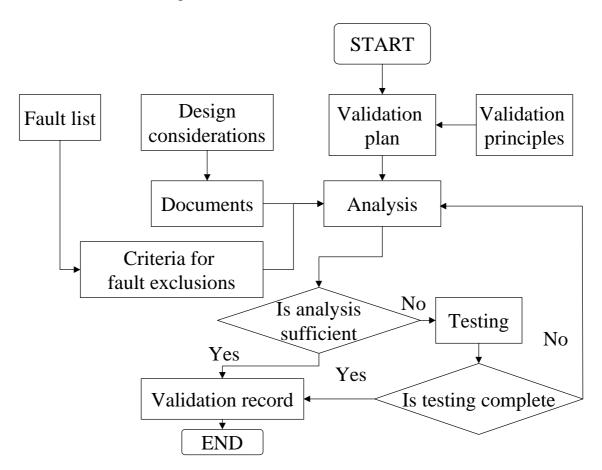

The phases of the validation process are presented in figure 1. First, the validation plan is made according to known validation principles. Then the system is analysed according to the validation plan, the known criteria, and the design considerations. Testing is carried out according to the validation plan and the results of the analysis. All the phases have to be recorded in order to have reliable proof of the validation process and the documents to help future modifications.

Figure 1. Overview of the validation process [prEN 954-2 1999]. When following the figure it is possible to go back from one state to earlier state.

### 2.2.1 Validation planning

The purpose of safety validation planning is to ensure that a plan is in place for the testing and analysis of the safety requirements (e.g. standards EN 954 or IEC 61508). Safety validation planning is also performed to facilitate and enhance the quality of safety validation. The planning shows the organisation and states in chronological order, the tests and verification activities needed in the validation process. A checklist is needed in the planning process in order to include all the essential analyses and tests into the safety validation plan. Such a checklist can be gathered from IEC 61508-1, prEN 954-2 or the Nordtest Method [Hérard et. al. 1999]. Large control systems may include separate subsystems, which are convenient to validate separately.

The main inputs for safety validation planning are the safety requirements. Each requirement shall be tested in the validation process and the passing criteria shall be declared in the plan. It is also important to declare the person(s) who makes the decisions if something unexpected happens, or who has the competence to do the validation. As a result, safety validation planning provides a guideline on how to perform safety validation.

### 2.2.2 Validation

The purpose of safety validation is to check that all safety related parts of the system meet the specification for safety requirements. Safety validation is carried out according to the safety validation plan. As a result of the safety validation, it is possible to see that the safety related system meets the safety requirements since all the safety requirements are validated. When discrepancies occur between expected and actual results it has to be decided whether to issue a request to change the system, or the specifications and possible applications. Also, it has to be decided whether to continue and make the needed changes later, or to make changes immediately and start the validation process in an earlier phase.

# 3 Safety issues related to complex components

### 3.1 Analysing strategy

The traditional way to analyse an electronic control system is to apply a bottom-up approach by using Failure Mode and Effect Analysis (FMEA, see 4.1.1). The method is effective and it reveals random failures well. The method is good for systems, which can be analysed thoroughly. Systems are, however, getting more complex and so the top-down approach is getting more and more applicable. A top-down approach like Fault Tree Analysis (FTA, see 4.1.2) helps to understand the system better and systematic failures can also be better revealed. The top-down approach also reveals well failures other than just random failures, which are better revealed by the bottom-up approach.

Another development due to increasing system complexity has been analysis on a module by module basis rather than on a component by component basis. Non-programmable electronic systems with moderate complexity can and should be analysed on a component by component basis and, in some cases (large systems), also on a module by module basis to cover complicated module/system level errors. To analyse complex programmable systems at the component by component basis by using bottom-up analysis (FMEA) would require a lot of resources and yet the method is not the best way to find certain failures. The system functions can be better understood at a module or system level than at a component level and so the quality of the analysis can be improved in that part.

The system analysis could be started from the bottom (not preferable) so that first each of the small subsystems are analysed and finally the system as a whole. In the so-called V-model, the system is designed from the top to the bottom (finest details) and then validated from the bottom to the top. The analysis should, however, be made as soon as possible during the design process in order to minimise possible corrections. Thereby the system should be analysed by starting from the top at system/module level. Then detailed component level analysis can be made in modules which were found critical at module level analysis. This method reduces the resources needed in the analysis. Table 1 illustrates the analysis activities at different levels.

Table 1. System, module and component level analysis and some aspects related to bottom-up analysis and top-down analysis.

| System level    | • Bottom-up analysis (e.g. FMEA) is useful and it reveals random failures well.                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | • Top-down method (e.g. FTA) illustrates the failures well, reveals sequential failures and human errors. Useful when the amount of top events is small. |

|                 | • At system level (without details) the analysis can often be made thoroughly.                                                                           |

|                 | • Validated modules can be used to ease the analysis.                                                                                                    |

| Module level    | • Bottom-up analysis is useful and it reveals random failures well.                                                                                      |

|                 | • Top-down method illustrates the failures well, reveals sequential failures and human errors. Useful when the amount of top events is small.            |

|                 | • Some hints for analysing standardised systems can be found.                                                                                            |

| Component level | • Bottom-up analysis can be laborious, but necessary for analysing low complexity systems and systems with high safety demands.                          |

|                 | • Top-down method or a mixture of top-down and bottom-up methods can be reasonable for analysing complex components, or systems with complex components. |

|                 | • Usually the system cannot be analysed thoroughly at system level.                                                                                      |

The common analysing strategy is bottom-up analysis on different levels, but it has some weak points, which have to be taken care of separately. The basic idea in FMEA is to analyse the system so that only one failure is considered at a time. However, common cause failures can break all similar or related components at the same time, especially if there is a miscalculation in dimensioning. These kind of failures have to be considered separately and then added to the analysis. If the safety demands are high, also sequential failures have to be considered carefully since FMEA does not urge the analyser to do so.

More and more often the bottom-up analysis tends to become too massive and laborious, so tactics are needed to minimise the work and amount of documentation. One strategy can be to document only critical failures. Another strategy can be to start the analysis on the most questionable (likely to be critical) structure and then just initially document the items and effects; the failure modes and other information are added only to critical failures. The FMEA table may then look rather empty, but it results in less work.

### 3.2 Complex modules and systems

### 3.2.1 Analysing strategy for modules and systems

Many complex components are at the present time too complex to be validated thoroughly (with reasonable resources) and programmable components are becoming even more complicated and specially tailored (e.g. ASIC, FPGA). This means that, for safety purposes, the systems including complex components have to cope with faults by being fault tolerant or by activating automatic safety functions; this can be achieved by concentrating on the architecture. Architecture can be best understood on a system/module level and, therefore, architectural weaknesses can also be conveniently revealed through a system or module level analysis . Additionally, on complex systems there are nearly always some design errors (hardware or software), which can be difficult to find at component level. At module level the analysis can be made thoroughly. One factor supporting module level analysis is the quality of the analysis. An increasing number of components in a unit to be validated corresponds to a reduction in the efficiency of the analysis. Although module level analysis is becoming more and more important, one cannot neglect the analysis at component level because certain failures can be better seen at the component level. A resource saving strategy is to concentrate on critical failures at all levels of analysis. The category (according to EN 954) or the SIL (according to IEC 61508) affects the detail to which the analysis should be performed.

Usually both system/module level and component level analyses are needed in validating complex systems. Analyses on system/module level are performed in order to determine the critical parts of the system, and component level analyses are carried out for those parts of the system.

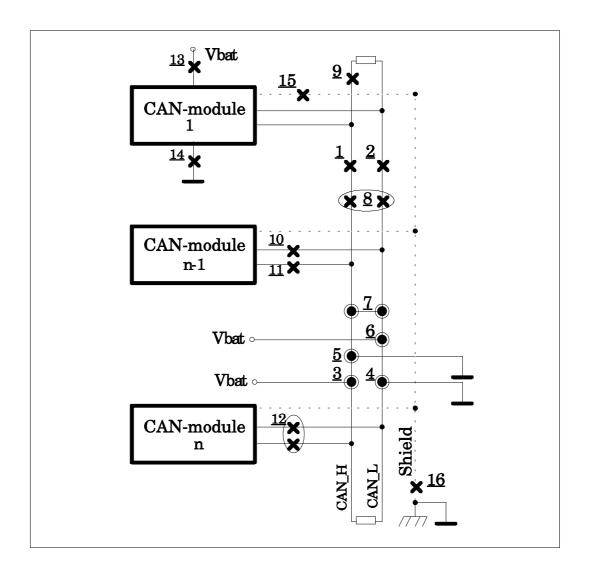

For module level analysis there are some references which give hints for failure modes of modules and for some standardised systems some advice for analysis can be found, CAN-bus is considered in appendix A as an example. For system/module level analysis, failure modes resemble failures at component level, however, the analyser has to consider the relevant failure modes.

### 3.2.2 Safety principles of distributed systems

Distributed systems are increasingly used in machinery. Distribution is normally realised by having multiple intelligent modules on a small area communication network. Each module may have several sensor inputs and actuator outputs. The trend, however, is to implement distributed systems with even smaller granularity, i.e. to have a network interface on single sensors or actuators.

Distribution helps to understand and grasp large systems better as the amount of wire is reduced<sup>1</sup> and the structure of the cabling is more comprehensible. Therefore, the number of mounting faults in a large system is most probably lower compared to a traditional centralised system. Hence, in regard to understandability and cabling simplicity, distributed systems introduce inherent dependability to some extent. Furthermore, in distributed systems it is easier to implement elaborate and localised diagnostic facilities as the system consists of several CPUs capable of doing both off-line and on-line monitoring and diagnostics<sup>2</sup>. The modularity of a distributed system also gives possibilities to implement 'limb home' capabilities in case of a failure in part of the system. These inherent characteristics of distributed systems increase the dependability of the system and therefore also affect the safety of the system in a positive way. However, distributed systems are always complex and hence bring along new kinds of safety problems and aspects, like:

- communication sub-system faults and errors (faults in cables, connectors, joints, transceivers, protocol chips or in the communication sub-system software; transient communication errors)

- communication sub-system design failures (like excessive communication delays, priority inversion and 'babbling idiot')

- system design failures (like scheduling errors or the nodes in the system may have a different view of time of the system state or of the state variables)

When designing distributed systems and busses, various safety techniques can be used to achieve the required safety and dependability level. There is not one ideal solution for all applications.

<sup>&</sup>lt;sup>1</sup> At least the total length of the wires is reduced, but the number of items (number of wires, connectors or joints, etc.) is not reduced in all cases.

<sup>&</sup>lt;sup>2</sup> It should, however, be noted that not all diagnostic facilities increase the dependability of the system compared to a less intelligent system; some diagnostic facilities must be implemented only to maintain the same level of dependability as that of the previous generation 'old-fashioned' control systems.

The analysing strategy described in section 3.1 can also be applied to complex components including distributed systems. In addition to this, distributed systems may have several architectural safety features and techniques for detection, avoidance and control of failures. Such safety principles are described in sections "Architectural principles" and "Detection, Avoidance and Control of Failures".

### Architectural Principles

Architectural principles crucially affect the safety performance of a safety critical distributed system. There are already some safety-validated busses, which are used for safety critical communication, and such systems always have redundancy and component monitoring. All fieldbusses have some kind of signal monitoring to reveal most of the errors in messages. In some cases the bus standard forces the use of certain architectural solutions. However, on higher level there are more architectural alternatives since large systems may have several different busses that are all used for adequate signalling. This section lists several architectural safety principles or techniques for distributed systems, and brings out the aim and description of each safety technique.

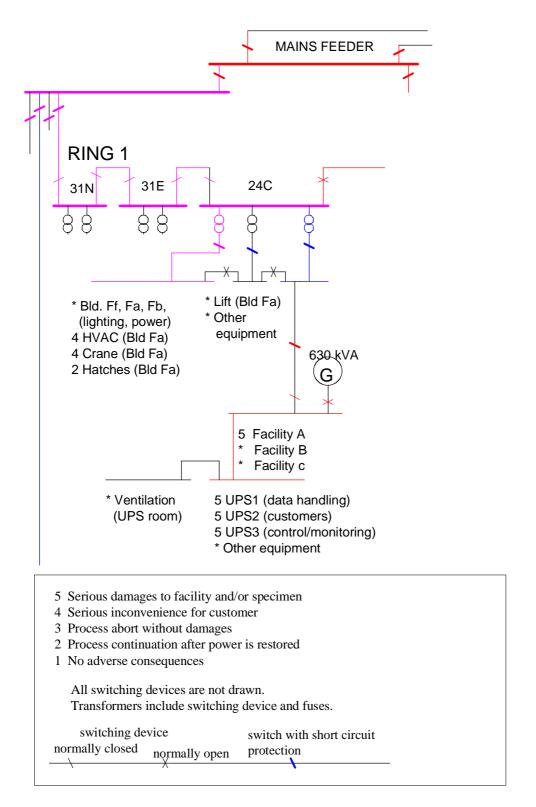

The architectural principles also have to be taken into account during the validation process. Distributed systems are so complex that many kinds of undetected component failures are possible. This means that the architecture of the system has to support fault tolerance and provide a way to force the system into a safe state in case of a failure. Table 2 lists some architectural principles, which should be considered both in the design and validation processes.

| Method                                                        | Applicability                                                                                                                                                                                                                                                |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware topology                                             | Hardware topology affects the safe performance of the system. It should be chosen so that in the weakest point the consequences are minimised.                                                                                                               |

|                                                               | <ul> <li>Redundant hardware topology detects failures by<br/>comparing signals between busses (See IEC 61508-7,<br/>A.7.3)</li> </ul>                                                                                                                        |

|                                                               | <ul> <li>Star topology can operate even if one node is faulty except<br/>if it is the node in the star point</li> </ul>                                                                                                                                      |

|                                                               | <ul> <li>Ring topology can operate even if there is a failure<br/>between two nodes [Kuntz, W. et al. 1993]</li> </ul>                                                                                                                                       |

|                                                               | <ul> <li>Redundant ring topology can operate in case of multiple<br/>failures in the communication system [Kuntz, W. et al.<br/>1993]</li> </ul>                                                                                                             |

|                                                               | <ul> <li>Power supply cabling star topology can supply power<br/>from the power source to other nodes even if one node<br/>fails or it's power cables break- provided that each node is<br/>fused separately.</li> </ul>                                     |

| Galvanic isolation<br>[DeviceNet<br>specification 1997]       | Galvanic isolation prevents different potential levels on distinct nodes to cause unwanted currents between the nodes.                                                                                                                                       |

|                                                               | <ul> <li>The communication lines and power supplies of the nodes<br/>are galvanically isolated with the help of optoisolators and<br/>DC/DC converters.</li> </ul>                                                                                           |

| Use of a dead man<br>switch line among<br>the bus cables [M3S | Dead man switch provides information to all nodes that the operator of the machine or vehicle is still controlling the system.                                                                                                                               |

| Specification 1995]                                           | <ul> <li>A single wire passing information from the dead man<br/>switch is included in the bus cabling and connectors. A<br/>total break in the bus cable should correspond to the<br/>situation that the operator is not controlling the system.</li> </ul> |

Table 2. Architectural principles.

### Table 2. Continued

| Method                                                                       | Applicability                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use of power<br>up/down line among<br>bus cables [M3S<br>Specification 1995] | <ul> <li>Use of a power up/down line gives a power up signal to all the nodes simultaneously and a power down signal in the case of power down or in an emergency.</li> <li>A single wire passing power up/down information is included in the bus cabling and connectors. A total break in the bus cable should correspond to the situation that the power down signal is active.</li> </ul> |

| Single wire<br>communication<br>[Pehrs 1992]                                 | Single wire communication offers capability to communicate<br>with single wire in case of malfunction in the other wire when<br>twisted pair communication is used.                                                                                                                                                                                                                           |

|                                                                              | <ul> <li>With the help of special transceiver circuitry<br/>communication can be continued with reduced signal-to-<br/>noise ratio in case of interrupt or short in the other twisted<br/>pair wire.</li> </ul>                                                                                                                                                                               |

| Redundant nodes<br>[Kopetz 1994]                                             | Redundant nodes enable continuous operation in the case of a node failure.                                                                                                                                                                                                                                                                                                                    |

|                                                                              | <ul> <li>Safety relevant nodes may be replicated to provide a<br/>backup node in the case of a failure, which may lead to an<br/>accident.</li> </ul>                                                                                                                                                                                                                                         |

| Global clock<br>[Gregeleit & Streich<br>1994]                                | <ul> <li>Global clock provides consistent view of time on all nodes.</li> <li>All the nodes of the system should keep an accurate copy of the system time in order to be able to perform time-synchronised operation.</li> </ul>                                                                                                                                                              |

| Shadow node<br>[Kopetz 1994]                                                 | <ul> <li>Shadow node provides a backup for services required in the system.</li> <li>A single node is arranged to provide the services of an impaired node or nodes. The shadow node works as a backup for multiple nodes.</li> </ul>                                                                                                                                                         |

Table 2. Continued

| Method                                                                             | Applicability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time triggered<br>communication<br>system<br>[Kopetz 1994]<br>[Lawson et al. 1992] | <ul> <li>Assures timeliness of state variables.</li> <li>To implement hard real-time control systems, an event based communication system may not be adequate to guarantee the timeliness of the state variables. In the time triggered approach, communication is scheduled in the design phase of the system prior to the operation. All activities on the bus as well as on the nodes are triggered by time not by events. Hence, the system is predictable and not controlled by stochastic events.</li> </ul> |

Detection, Avoidance and Control of Failures

This section includes several failure detection, avoidance and control techniques for distributed systems (Table 3). The aims and the main features of each technique are brought out. When the person who analyses the distributed system recognises any of the safety techniques concerning failure detection, avoidance or control, he should observe, what the capabilities of each technique are in order to enhance the safety of the system.

| Method                           | Applicability                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cyclic Redundancy<br>Check (CRC) | <ul> <li>Errors in received data can be detected by applying CRC over the transferred data.</li> <li>The transmitter appends a CRC code to the end of the data frame. The receiver should get the same CRC value as a result when applying the same CRC algorithm (polynomial) to the data of the frame. If the CRC value calculated by the receiver differs from that of the one received in the transmitted frame, the data is regarded as erroneous.</li> </ul> |

### Table 3. Continued

| Method                                                                                                         | Applicability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communication<br>error recovery by<br>retransmission<br>[Kopetz 1994]<br>[ISO 11898]                           | Retransmission ensures reliable transfer of data in case of<br>transient failures during transmission.<br>Messages that are discarded by some of the nodes are<br>retransmitted.<br>Note! This may cause non-deterministic communication<br>latencies if there is no way to control the retransmission<br>process.                                                                                                                                                                                                                  |

| Message replication<br>without hardware<br>redundancy [Kopetz<br>et al. 1989] (see also<br>IEC 61508-7, A.7.6) | <ul> <li>Replicating the message by sending it twice or more allows loss of N-1 messages if the message is sent N times.</li> <li>Always sending the message twice or more sequentially over a single bus allows deterministic timing compared to that of retransmission in case of failure. If the message is sent twice and the receiver receives the two messages but with different data, both messages must be discarded. If the number of replicated messages is for example three, 2 out of 3 voting can be used.</li> </ul> |

| Monitoring shorts or<br>open circuits of the<br>bus wires [Pehrs<br>1992], [Tanaka et al.<br>1991]             | <ul> <li>Monitoring shorts or open circuits activates corrective or safety functions in case of a total communication blackout.</li> <li>The bus wires are monitored by hardware and signalled to software in case of a malfunction.</li> </ul>                                                                                                                                                                                                                                                                                     |

| Monitoring bus load<br>[DIN 9684 Teil 3<br>1993]                                                               | <ul> <li>Monitoring bus load enables bus traffic to be restricted dynamically in case of excessive bus load.</li> <li>The message rate is monitored by software and if the rate is too high, the nodes are forced to apply inhibit times in their transmission processes.</li> </ul>                                                                                                                                                                                                                                                |

| Monitoring presence<br>of relevant nodes<br>[CiA/DS301 1999]                                                   | Monitoring presence of relevant nodes expose accidental<br>drop-out of a node.<br>Some of the nodes or all nodes monitor the presence of<br>relevant nodes with the help of periodic messages.                                                                                                                                                                                                                                                                                                                                      |

### Table 3. Continued

| Method                                                                                  | Applicability                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Restricting<br>transmission period<br>of messages [DIN<br>9684 Teil 3 ]                 | <ul> <li>Restricting transmission period disables excessive bus load<br/>and thus guarantees proper message latencies for all messages.</li> <li>All the nodes of the system are forced to apply specific<br/>transmission rate rules in their transmission processes.</li> </ul>                                                                                                                                                                |

| Babbling idiot<br>avoidance [Tindell<br>et al. 1995]                                    | <ul> <li>Babbling idiot avoidance prevents a single or several nodes from sending erroneously a lot of (high priority) messages, thus gaining exclusive bus access.</li> <li>The communication software of a node should not be able to enter such a mode. Hence the software should be carefully designed and analysed in order to avoid this type of situation. Runtime monitoring can be done together with hardware and software.</li> </ul> |

| Priority inversion<br>avoidance                                                         | <ul> <li>Messages are controlled so that a low priority message cannot prevent a high priority message from entering the bus.</li> <li>This type of situation occurs locally on a node if a low priority message enters the bus contest first and blocks the higher priority message. The situation can be avoided by software and sophisticated hardware, or by time triggered message scheduling.</li> </ul>                                   |

| Message scheduling<br>based on inhibit<br>times [Fredriksson<br>1995]                   | <ul> <li>Message scheduling based on inhibit times ensures timeliness of the relevant messages on the communication bus.</li> <li>Messages are scheduled by introducing inhibit times to communication objects, thus guaranteeing bus access for low priority message. This method can be used in event based bus systems.</li> </ul>                                                                                                            |

| Time<br>synchronisation<br>[Fredriksson 1995],<br>[Lawson et al. 1992]<br>[Kopetz 1994] | <ul> <li>Time synchronisation ensures timeliness of all the messages<br/>on the communication bus.</li> <li>Messages are scheduled by synchronising the transmission<br/>of a message with respect to time.</li> </ul>                                                                                                                                                                                                                           |

| Time stamping                                                                           | <ul> <li>Time stamping enables the evaluation of the validity of the data or helps to recognise varying communication delays.</li> <li>The arrival time of a message is stored.</li> </ul>                                                                                                                                                                                                                                                       |

### Table 3. Continued

| Method                                                        | Applicability                                                                                                                                                                                                                                             |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Consistency control<br>of state variables<br>[ISO 11898 1993] | Consistency control of state variables ensures that there is no discrepancy between data (and system state) on different nodes.                                                                                                                           |

|                                                               | <ul> <li>The communication protocol should be such that all the<br/>nodes accept the correct data from the bus at the same<br/>time. If one of the nodes receives incorrect data, all the<br/>nodes should discard the data.</li> </ul>                   |

| Configuration check                                           | Configuration check ensures that correct hardware and software versions are used on the nodes of the system.                                                                                                                                              |

|                                                               | <ul> <li>A single node (master) or multiple nodes may check in<br/>start-up, with a help of a request message, if the relevant<br/>nodes use the presumed hardware and software and<br/>parameter versions.</li> </ul>                                    |

| End-to-end CRC<br>[Kopetz 1994]                               | End-to-end CRC can be used to detect data errors beyond bus communication errors.                                                                                                                                                                         |

|                                                               | <ul> <li>Normal CRC checks the data integrity between message<br/>transmission and receiving, but the end-to-end CRC also<br/>checks data integrity from sensor measurement to message<br/>transmission and from message arrival to actuation.</li> </ul> |

| Message numbering                                             | Message numbering ensures correct assembly of the received<br>stream of segmented data or enables discarding of duplicated<br>messages.                                                                                                                   |

|                                                               | <ul> <li>Consecutive messages are numbered, in order to be able to<br/>detect discontinuities in the data block or replication of<br/>data segments. Numbering can often be accomplished<br/>only with a single bit (toggle bit).</li> </ul>              |

### 3.3 Complex components

Complex components hold more than 1000 gates and/or more than 24 pins [prEN 954-2 1999]. The definition only provides a rough estimate as to which component could be complex. The amount of potentially different random failures in such a component is large. Only the number of combinations two out of 24 is 276 and this is just the amount of simple short circuits in a small (according to the definition) complex component.

Complex components have several failure modes. If one blindly analyses all combinations then this would result in many irrelevant failures. Failure exclusions are needed in order to focus the resources on the critical failures.

### 3.3.1 Failure modes for complex components

Table 4 shows the random failures of the complex components according to prEN 954-2. The table clearly shows all failures related to the input or output of the circuit. The exclusions column shows if it is possible to ignore certain type of failures; so "No" means that the failure mode has to be considered in all cases.

Table 4. Faults to be considered with programmable or complex integrated circuits. [prEN 954-2 1999].

| Faults considered                                                                                                             | Exclusions                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Faults of part or all of the function (see a and b)                                                                           | No (see a)                                                                                                                                                   |  |  |

| The fault may be static, change the logic, be dependent<br>on bit sequences                                                   |                                                                                                                                                              |  |  |

| Open-circuit of each individual connection                                                                                    | No                                                                                                                                                           |  |  |

| Short circuit between any two connections (see c)                                                                             | No                                                                                                                                                           |  |  |

| Stuck-at-fault; static "0" and "1" signal at all inputs<br>and outputs either individually or simultaneously (see<br>c and d) | No                                                                                                                                                           |  |  |

| Parasitic oscillation of outputs (see e)                                                                                      | No<br>A fault exclusion can be<br>justified, if such an oscillation<br>cannot be simulated by<br>realistic parasitic feedback<br>(capacitors and resistors). |  |  |

| Changing value (e.g. in/output voltage of analogue devices)                                                                   | No                                                                                                                                                           |  |  |

| Undetected faults in the hardware which are unnoticed because of the complexity of the integrated circuit (see a and b)       | No                                                                                                                                                           |  |  |

### Table 4. Continued

### Remarks

a - Faults in memory circuits and processors shall be avoided by self-tests, e.g. ROM-tests, RAM-tests, CPU-tests, external watchdog timers and the complete structure of the safety related parts of the control system.

b - The faults considered give only a general indication for the validation of programmable or complex integrated circuits

c - Because of the assumed short-circuits in an integrated circuit, safety signals need to be processed in different integrated circuits separated when redundancy is used.

d - i.e. short circuit to 1 and 0 with isolated input or disconnected output.

e - Frequency and the pulse duty factor dependent on the switching technology and the external circuitry. When testing, the driving stages in question are disconnected

However, the basic failures to be considered in the analysis can be simple compared to the actual failures that can happen inside the component. Such component specific failures can for example be, a failure in the microprocessor register or a failure in a certain memory location.

In the draft IEC 61508-2, failures typical to certain component technology (e.g. CPU, memory, bus) are considered instead of the pins (input, output etc.) of the component. A single component can include several technologies.

Table 5 shows some component dependent failures. The table is gathered from draft IEC 61508-2 and the listed failure modes need to be considered when the diagnostic coverage is high<sup>3</sup>. [IEC 61508-2 1997]

$<sup>^{3}</sup>$  =fractional decrease in the probability of dangerous hardware failure resulting from operation of the automatic diagnostic tests [IEC 61508-4:1998]

| Component                                                            | Faults or failures to be detected                                                                                                                                                                                    |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                                                                  |                                                                                                                                                                                                                      |

| – register, internal RAM                                             | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines- all these for<br>data and addresses;<br>dynamic cross-over for memory cells;<br>no wrong or multiple addressing |

| <ul> <li>coding and execution<br/>including flag register</li> </ul> | no definite failure assumption;                                                                                                                                                                                      |

| <ul> <li>address calculation</li> </ul>                              | no definite failure assumption;                                                                                                                                                                                      |

| <ul> <li>program counter, stack</li> <li>pointer</li> </ul>          | Stuck-at faults, stuck-open, open or high impedance outputs, short-circuits between signal lines.                                                                                                                    |

| Bus                                                                  |                                                                                                                                                                                                                      |

| – general                                                            | time out;                                                                                                                                                                                                            |

| <ul> <li>memory management<br/>unit</li> </ul>                       | wrong address decoding;                                                                                                                                                                                              |

| <ul> <li>direct memory access</li> </ul>                             | all faults which affect data in the memory; wrong data or addresses; wrong access time;                                                                                                                              |

| – bus-arbitration (see <i>a</i> )                                    | no or continuous or wrong arbitration.                                                                                                                                                                               |

| Interrupt handling                                                   | no or continuous interrupts;<br>cross-over of interrupts.                                                                                                                                                            |

| Clock (Quartz)                                                       | sub- or superharmonic.                                                                                                                                                                                               |

| Invariable memory                                                    | all faults which affect data in the memory.                                                                                                                                                                          |

| Variable memory                                                      | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines - all these for<br>data and addresses; dynamic cross-over for memory cells;<br>no wrong or multiple addressing.  |

| Discrete hardware                                                    |                                                                                                                                                                                                                      |

| – digital I/O                                                        | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines;<br>drift and oscillation.                                                                                       |

| – analogue I/O                                                       | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines;<br>drift and oscillation.                                                                                       |

| <ul> <li>power supply</li> </ul>                                     | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines;<br>drift and oscillation.                                                                                       |

| Communication and mass                                               | all faults which affect data in the memory;                                                                                                                                                                          |

| storage                                                              | wrong data or addresses; wrong transmission time;<br>wrong transmission sequence.                                                                                                                                    |

| Electromechanical devices                                            | does not energise or de-energise; individual contacts<br>welded, no positive guidance of contacts, no positive<br>opening.                                                                                           |

Table 5. Faults or failures of complex components.

### Table 5. Continued

| Component                                                                                                                                                                                                                                                  | Faults or failures to be detected                                                                                              |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sensors                                                                                                                                                                                                                                                    | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines;<br>drift and oscillation. |  |  |  |  |

| Final elements                                                                                                                                                                                                                                             | Stuck-at faults, stuck-open, open or high impedance<br>outputs, short-circuits between signal lines;<br>drift and oscillation. |  |  |  |  |

| <ul> <li><i>a</i> - Bus-arbitration is the mechanism for deciding which device has control of the bus.</li> <li><i>b</i> - "stuck-at" is a fault category which can be described with continuous "0" or "1" or "on" at the pins of a component.</li> </ul> |                                                                                                                                |  |  |  |  |

### 3.3.3 Safety aspects

It is obvious that the person validating the system has to decide which possible failures have to be documented. Usually an expert can see from the circuit diagram which failures can cause severe effects, but generic rules how to neglect some failures can be hard to find. For some standardised technologies it is possible to find in advance the critical failures to consider. This minimises the amount of failures to be considered, and improves the quality of the analysis.

Systematic failures related to complex components and complex systems become even more obvious. There are errors in most commercial programs (usually more than 1/1000 code lines), but usually the errors appear relatively seldomly [Gibbs 1994]. The validation of software is described in IEC 61508-3 [IEC 61508-3 1998].

Hardware design failures are probable in complex components and especially in tailored components. Consequently, in complex systems, systematic errors are more common than random failures. The whole system has to be validated and both systematic and random failures have to be considered.

Appendix A shows as an example what kind of failures are related to CAN-bus. Most of the described failures can be used with other types of distributed systems, but the analyser has to know the special features related to the system that is under consideration.

# 4 Methods of analysis4.1 Common analysis methods

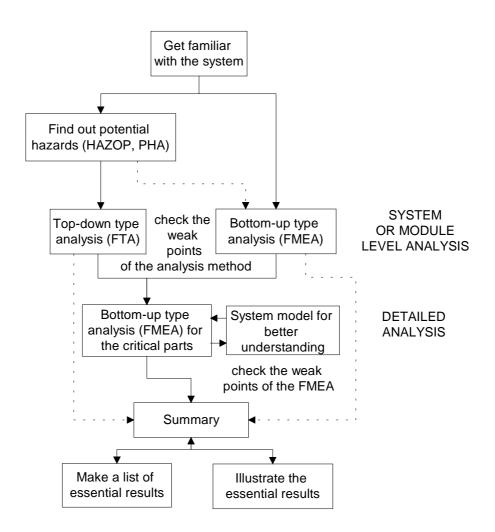

Different analysing techniques are needed in different phases of the design. At first, hazard identification and risk analysis techniques are useful, for example techniques such as, "Hazard and Operability study (HAZOP)", "Preliminary Hazard Analysis (PHA)", and techniques which use hazard lists. There are many techniques for software verification and for probabilistic approach to determine safety integrity. In software verification the software errors are searched systematically by using for example data flow analysis, control flow analysis, software FMEA, or sneak circuit analysis (see IEC 61508-7). In probabilistic approach, it is expected that the verification process has already been carried out, and statistical values are used to calculate a probabilistic value for executing the program correctly. There are also methods for verifying components, such as ASIC, designs. This chapter, however, is concentrating on analysis techniques which are used in analysing control systems.

There are two basic types of techniques for analysing systems:

- Top-down methods (deductive), which begin with defined system level top event(s) and the initiating factors are concluded.

- Bottom-up methods, which begin with single failures and the system level consequences are concluded.

Both analysing techniques have their advantages and disadvantages, but ultimately the value of the results depend on the analyst. The techniques can, however, make the analyst more observant to detect certain type of failures or events. Bottom-up methods tend to help the analyst to detect all single failures and events, since all basic events are considered. Top-down methods tend to help the analyst to detect how combined effects or failures can cause a certain top event. Top-down methods are good only if the critical events have to be analysed. Bottom-up methods are good if the whole system has to be analysed systematically. The basic demand is that the analysing technique must be chosen so that all critical events are to be detected with the minimum duty. Top-down methods give an overview of the system, show the critical parts, systematic failures and human factors. Bottom-up methods consider the system systematically and many failures are found.

A combined bottom-up and top-down approach is often likely to be an efficient technique. The top-down analysis provides the global picture and can focus the analysis to areas that are most significant from the overall performance point of view. Bottom-up

methods can then be focused on the most critical parts. Bottom-up analysis aims at finding "the devil that hides in the details".

The most important point after choosing the analysing method is to concentrate on the weak points of the method, and this can be done by using strict discipline. The weak points of FMEA and FTA are described in chapters 4.1.1 and 4.1.2.

### 4.1.1 FMEA

When the safety and performance of a control system is assessed, the Failure Mode and Effect Analysis (FMEA) is the most common tool used. An international standard (IEC 812. 1985) exists to defines the method. FMEA is a bottom-up (inductive) method, which begins with single failures, and then the causes and consequences of the failure are considered. In the FMEA, all components, elements or subsystems of the system under control are listed. FMEA can be done on different levels and in different phases of the design which affects the depth of the analysis. In an early phase of the design, a detailed analysis cannot be done, and also some parts of the system can be considered so clear and harmless that deep analysis is not seen as necessary. However, in the critical parts, the analysis needs to be deep and it should be made on a component level. If the safety of the system really depends on a certain complex component, the analysis may even include some inner parts of the component, for example this can mean software analysis or consideration of typical failures related to a certain logical function.

In prEN 954-2 there are useful lists for FMEA on failures of common components in different types of control systems. The standard gives probable component failures and the analyst decides if the failures are valid in the system considered or if there are other possible failures. If functional blocks, hybrid circuits or integrated circuits are analysed then the list in prEN 954-2 is not enough. Additionally, systematic failures and failures typical to the technology (microprocessors, memories, communication circuits etc.) have to be considered since those failures are more common than basic random hardware failures.

FMEA is intended mainly for single random failures and so it has the following weak points:

- It does not support detection of common cause failures and design failures (systematic failures).

- Human errors are usually left out; the method concentrates on components and not the process events. A sequence of actions causing a certain hazard are difficult to detect.

- Sequential failures causing a hazard can also be difficult to detect, since the basic idea of the method is to consider one failure at a time. If the analysis is made with strict discipline it is also possible to detect sequential failures. If a failure is not detected by the control system, other failures (or events) are studied assuming the undetected failure has happened.

- Systems with a lot of redundancy can be difficult to consider since sequential failures can be important.

- The method treats failures equally, and so even failures with very low probability are considered carefully. This may increase the workload and cause a lot of paperwork.

- In a large analysis documentation, it can be difficult to identify the critical failures.

It can be difficult to see which failures have to be considered first, and what the best means are to take care of the critical failures.

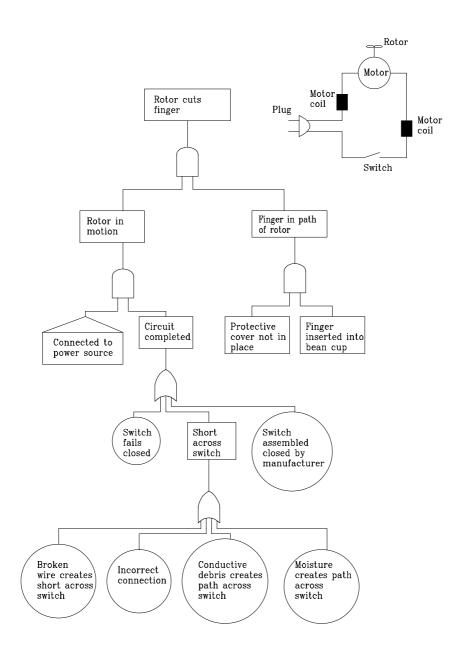

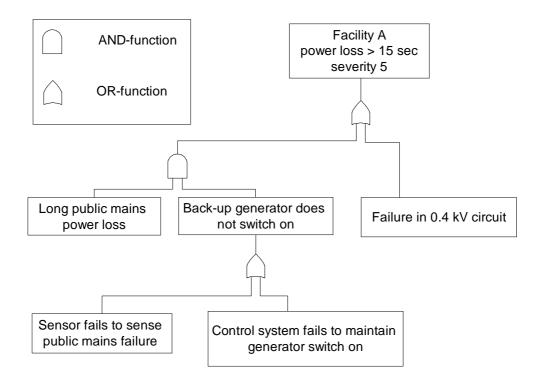

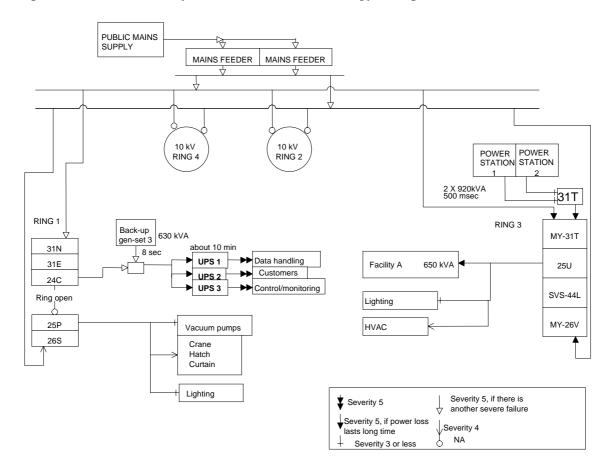

However, FMEA is probably the best method to detect random hardware failures, since it considers all components (individually or as blocks) systematically. Some critical parts can be analysed on a detailed level and some on a system level. If the method seems to become too laborious, the analysis can be done on a higher level, which may increase the risk that some failure effects are not detected.